AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

Revolutionary Quad-Pipelined Ultra High Performance Microcontroller

The DQ8051CPU is delivered with fully automated testbench and complete set of tests, allowing easy package validation at each stage of SoC design flow.

Each of 8051 cores has a built-in support for Hardware Debug System, called DoCDTM. It is a real-time hardware debugger, which provides debugging capability of a whole System on Chip (SoC).

Unlike other on-chip debuggers, the DoCDTM provides non-intrusive debugging of running application. It can halt, run, step into or skip an instruction, read/write any contents of the microcontroller, including all registers, internal and external program memories, all SFRs, including user defined peripherals.

View Revolutionary Quad-Pipelined Ultra High Performance Microcontroller full description to...

- see the entire Revolutionary Quad-Pipelined Ultra High Performance Microcontroller datasheet

- get in contact with Revolutionary Quad-Pipelined Ultra High Performance Microcontroller Supplier

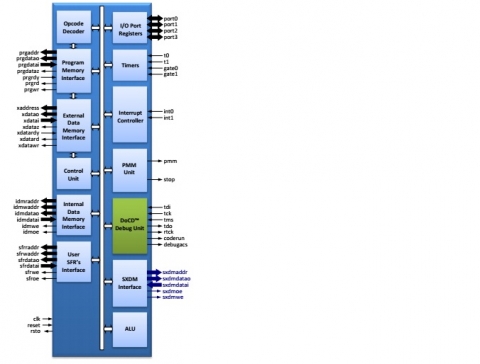

Block Diagram of the Revolutionary Quad-Pipelined Ultra High Performance Microcontroller

8051 IP IP

- Pipelined High Performance Microcontroller

- Super-Fast 8051 Microcontroller Core with Configurable Features and Peripherals

- High Performance 8051 Compatible CPU Core

- Instruction Set Compatible with the 8051 8-bit Microcontroller Architecture

- High Performance / Low Power Microcontroller Core

- Intel™ 8051 8-bit Microcontroller