RISC-V Platform-Level Interrupt Controller (PLIC) IP

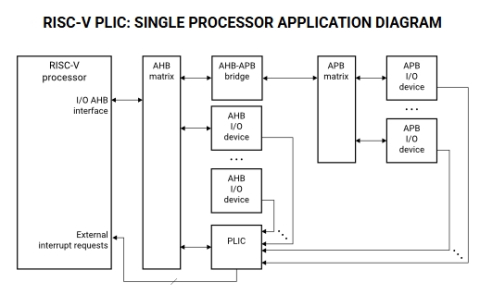

In a single-processor application, the PLIC connects to the AHB bus matrix and collects interrupt requests for AHB and APB I/O devices. The PLIC target interrupt requests connect to the RISC-V processor’s external interrupt request inputs, providing interrupts for machine-mode and user-mode contexts.

In a larger multiprocessor application, the PLIC connects to the shared AHB bus matrix and collects interrupt requests for AHB and APB I/O devices. The PLIC treats each execution context (machine mode, supervisor mode, user mode) on each processor as a separate target for interrupts. An interrupt can be enabled for multiple targets. The first processor to claim the interrupt by reading the corresponding PLIC claim register is responsible for handling the interrupt and for indication completion to the PLIC.

View RISC-V Platform-Level Interrupt Controller (PLIC) IP full description to...

- see the entire RISC-V Platform-Level Interrupt Controller (PLIC) IP datasheet

- get in contact with RISC-V Platform-Level Interrupt Controller (PLIC) IP Supplier

Block Diagram of the RISC-V Platform-Level Interrupt Controller (PLIC) IP