MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes in TSMC (N5, N3E, N3P)

RSA IP Core

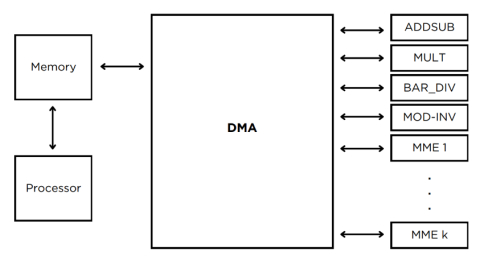

RSA IP cores consist of a cluster of IPs. VHDL is used as the Hardware Description Language of the IP Cores. The cluster includes ADDSUB (Addition and substruction), MULT (Multiplication), BAR_DIV (Barrett Divider), MOD_INV (Modulo Inversion) and MME (Montgomery Modulo Exponentiation) IP Cores. MME cores are configurable, and their number can be changed.

View RSA IP Core full description to...

- see the entire RSA IP Core datasheet

- get in contact with RSA IP Core Supplier

Block Diagram of the RSA IP Core IP Core

RSA IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable Public Key Cryptographic (RSA, ECDSA, SM2, Diffie-Hellman) accelerator - optional SCA protection

- RSA Keygen IP Core

- Java Card compliant cryptographic library for encryption and decryption of RSA, DSA, Diffie-Hellman, El-Gamal and Elliptic Curves algorithms

- Hardware accelerator for RSA, DSA, Diffie-Hellman, El-Gamal and Elliptic Curves algorithms

- Secure cryptographic library compliant with the X9.31 and FIPS 186-4 standards.