5V Library for Generic I/O and ESD Applications TSMC 12NM FFC/FFC+

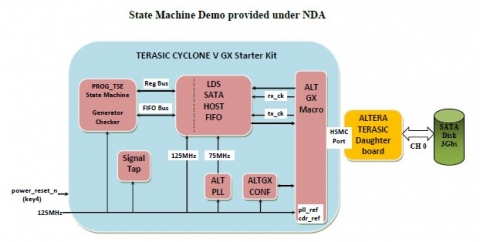

SATA 2 HOST ON CYCLONE 5 GX

View SATA 2 HOST ON CYCLONE 5 GX full description to...

- see the entire SATA 2 HOST ON CYCLONE 5 GX datasheet

- get in contact with SATA 2 HOST ON CYCLONE 5 GX Supplier

Block Diagram of the SATA 2 HOST ON CYCLONE 5 GX IP Core