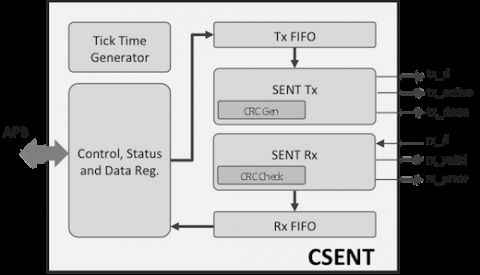

SENT/SAE J2716 Controller

The CSENT core can be configured as a Transmitter and/or as a Receiver, and therefore it is suitable for adding a SENT interface to devices transmitting sensor data or to controllers receiving sensor data. It provides access to its control, status, and data registers via a 32-bit APB bus interface, and a comprehensive set of interrupt signals facilitates interrupt-based operation. The core allows for Transmitter operation without requiring any external programming or control. The reset values for all its control registers are defined at synthesis time, and at run time the system only needs to write sensor data to the core.

The CSENT core is designed with industry best practices. The core contains no latches or tri-sates, and is fully synchronous with a single clock domain. The core is available in Verilog RTL or as targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

View SENT/SAE J2716 Controller full description to...

- see the entire SENT/SAE J2716 Controller datasheet

- get in contact with SENT/SAE J2716 Controller Supplier

Block Diagram of the SENT/SAE J2716 Controller IP Core