Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

Serial FIR Filter

The Lattice Serial FIR filter uses serial arithmetic elements to achieve a compact size. Due to the serial nature of the arithmetic, the data rate is slower than the clock rate and dependant on the data width. The effective throughput is defined as:

Data rate = (f/(ofw +1)

where ofw is the Output Full Width and f is the clock frequency.

View Serial FIR Filter full description to...

- see the entire Serial FIR Filter datasheet

- get in contact with Serial FIR Filter Supplier

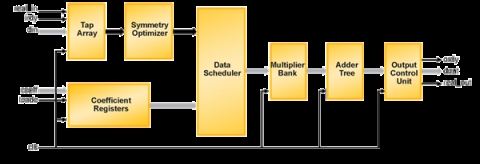

Block Diagram of the Serial FIR Filter IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software