SGMII and Gb Ethernet PCS

The Serial Gigabit Media Independent Interface (SGMII) is a connection bus for Ethernet Media Access Controllers (MACs) and Physical Layer Devices (PHYs) defined by Cisco Systems. It replaces the classic 22-wire GMII connection with a low pin count, 4-pair, differential SGMII connection. The classic GMII interface defined in the IEEE802.3 specification is strictly for Gigabit rate operation. However, the Cisco SGMII specification defines a method for operating 10 Mbps and 100 Mbps MACs over the interface. Moreover, the Cisco SGMII specification is comprised of more than just a bus interface definition; it defines a bridging function between SGMII and GMII buses.

These applications can be completely implemented in ECP5, LatticeECP3™, LatticeECP2M™ and LatticeSC™ Field Programmable Gate Array (FPGA) devices. As an example, Lattice has developed a reference design for a complete SGMII-to-(G)MII bridge. This reference design is included with the SGMII and Gb Ethernet PCS IP Core package and is described in detail in Appendix C.

The core can be instantiated, synthesized and simulated through IPexpress™ software.

View SGMII and Gb Ethernet PCS full description to...

- see the entire SGMII and Gb Ethernet PCS datasheet

- get in contact with SGMII and Gb Ethernet PCS Supplier

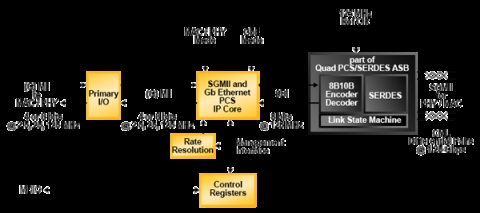

Block Diagram of the SGMII and Gb Ethernet PCS IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software