SHA1, SHA2 Cryptographic Hash Cores

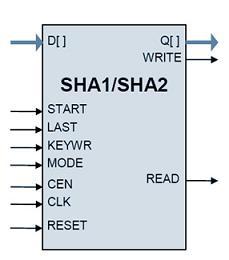

The cores utilize “flow-through” design that can be easily included into the data path of a communication system or connected to a microprocessor: the core reads the data via the D input and outputs the hash result via its Q output. Data bus widths for both D and Q are parameterized.

The design is fully synchronous and is available in both source and netlist form.

View SHA1, SHA2 Cryptographic Hash Cores full description to...

- see the entire SHA1, SHA2 Cryptographic Hash Cores datasheet

- get in contact with SHA1, SHA2 Cryptographic Hash Cores Supplier

Block Diagram of the SHA1, SHA2 Cryptographic Hash Cores IP Core