Secure-IC's Securyzr™ Tunable Hash (SHA1-SHA2) Hardware accelerator

SLVS-EC Interface for FPGA

* Altera® FPGAs can receive signals directly from the SLVS-EC Interface.

* Compatible with the latest SLVS-EC Specification Version 3.0.

* Supports powerful De-Skew function. Enables board design without considering Skew that occurs between lanes.

* "Evaluation kit”(see below) is available for speedy evaluation at the actual device level.

View SLVS-EC Interface for FPGA full description to...

- see the entire SLVS-EC Interface for FPGA datasheet

- get in contact with SLVS-EC Interface for FPGA Supplier

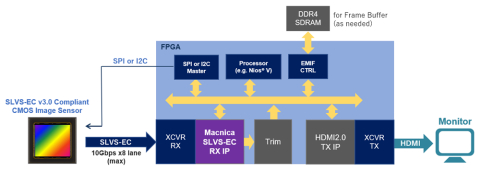

Block Diagram of the SLVS-EC Interface for FPGA IP Core

SLVS-EC interface IP

- Camera SLVS-EC 3.0 Receiver 10.0Gbps 8-Lane

- Camera SLVS-EC/MIPI D-PHY/sub-LVDS/CMOS1.8 combo Receiver 5.0G/2.5G/1Gbps/166MHz 8-Lane

- Camera SLVS-EC 2.0 Receiver 5.0Gbps 8-Lane

- Camera SLVS-EC 3.0 Transmitter 10.0Gbps 8-Lane

- Camera SLVS-EC v.2.0 5.0Gbps / MIPI D-PHY v2-1 4.5Gbps combo Receiver 4-Lane

- Camera SLVS-EC/MIPI D-PHY/sub-LVDS/CMOS1.8 combo Receiver 2.4G/2.5G/800Mbps/166MHz 8-Lane