Sony Camera LVDS Interface

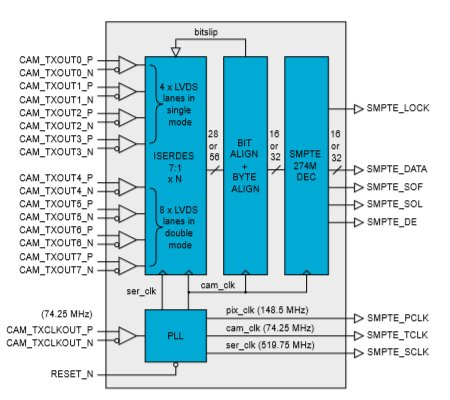

The interface supports both single-mode and double-mode operation in which 4 x LVDS data lanes or 8 x LVDS data lanes may be connected to the IP Core. In the standard configuration, the camera input clock (TXCLKOUT_P/N) is assumed to be set to a frequency of 74.25 MHz. This permits operation at HD1080p30 resolution in single-mode (1x16-bit pixels per clock) or HD1080p60 operation in double-mode (2x16-bit pixels per clock).

The LVDS data lanes are deserialized using the high-speed SERDES input resources of the FPGA.. The resulting parallel data are then aligned and decoded to provide a standard SMPTE 274M output video stream. SMPTE data changes on the rising-clock edge of the SMPTE_TCLK (cam_clk) signal.

Other flags are also provided to indicate the presence of active video, the start of an active frame and the start of an active line. In addition, there is a stream locked flag that indicates the bit alignment has succeeded and a valid SMPTE stream has been found.

View Sony Camera LVDS Interface full description to...

- see the entire Sony Camera LVDS Interface datasheet

- get in contact with Sony Camera LVDS Interface Supplier

Block Diagram of the Sony Camera LVDS Interface IP Core