MIPI D-PHY Tx v1.1 ONLY @1.5ghz Ultra Low Power & Low Area for IoT & Wearables

SPI Slave to AHB Lite Master

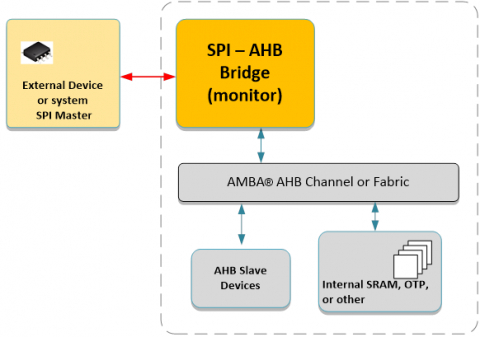

A SPI Slave to AHB Lite Interface block provides read/write access by an external SPI device to the various memories and registers that are present in the chip's internal AHB Lite subsystem. The Bridge converts SPI transactions into AHB Read or Write instructions, allowing the external SPI device to have full access to all memory mapped devices present in the AHB Lite subsystem.

The SPI protocol layer is responsible for several things including:

- Interpreting commands from the low-level SPI interface (R/W, address, mode, protection, burst length).

- Generating an AHB Read or Write transaction based on the command

received from the SPI interface.

- Presenting (parallel) address and write data from the low-level SPI interface to the system.

- Presenting (parallel) read data from the system to the low-level SPI interface.

View SPI Slave to AHB Lite Master full description to...

- see the entire SPI Slave to AHB Lite Master datasheet

- get in contact with SPI Slave to AHB Lite Master Supplier

Block Diagram of the SPI Slave to AHB Lite Master

Bridge IP

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- General Purpose & Bridge DMA

- RapidIO to AXI Bridge (RAB)

- Digital Capacitive Plus Bridge Sensor Interfaces