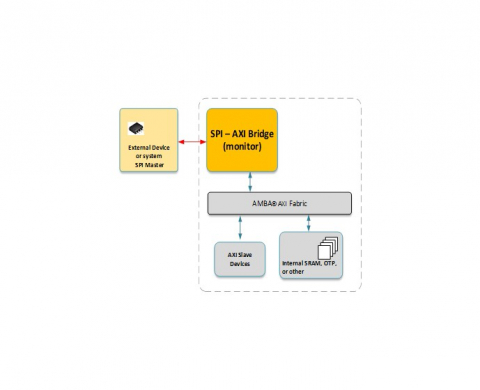

SPI Slave to AXI Bridge

Logic on two synchronous clock domains is used to accomplish the translation.

The AHB Lite logic is responsible for responding to transaction requests from the AHB Lite, and for generating AXI transactions based on transaction information from the AHB logic, and for presenting read data from the AXI subsystem back to the AHB Lite Master.

The AXI logic is responsible for generating AXI transactions based on transaction information from the AHB Lite logic, and for pacing the AXI transaction based on internal FIFO levels and on responses from the AXI Slave peripheral.

The AHB Lite to AXI Bridge acts as an AHB Lite Slave, and an AXI Master in an AXI/AHB subsystem. Typically, the AHB Lite to AXI Bridge has its AHB Lite interface connected to a Slave port on an AHB Lite Channel/Interconnect module, and its AXI interface connected to the Master port on an AXI Channel module.

View SPI Slave to AXI Bridge full description to...

- see the entire SPI Slave to AXI Bridge datasheet

- get in contact with SPI Slave to AXI Bridge Supplier

Block Diagram of the SPI Slave to AXI Bridge IP Core

Bridge IP

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- General Purpose & Bridge DMA

- RapidIO to AXI Bridge (RAB)

- Digital Capacitive Plus Bridge Sensor Interfaces