Tensilica AI Boost

The product architecture natively supports the most common network layers found in these applications including convolution, depth-wise separable convolution, fully connected, LSTM, pooling, reshaping, and concatenation layers. Other layers can be support

View Tensilica AI Boost full description to...

- see the entire Tensilica AI Boost datasheet

- get in contact with Tensilica AI Boost Supplier

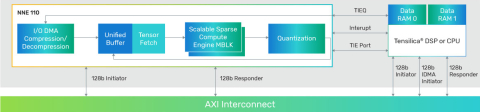

Block Diagram of the Tensilica AI Boost IP Core

AI boost IP

- NPU IP family for generative and classic AI with highest power efficiency, scalable and future proof

- RISC-V Tensor Unit

- 64-bit CPU with RISC-V Vector Extension

- 64-bit CPU with RISC-V Vector Extension

- High performance dual-issue, out-of-order, 7-stage Vector processor (DSP) IP

- High performance dual-issue, out-of-order, 7-stage pipeline superscalar core