TSMC 22nm ULL Wirebond/Flipchip I/O Library with switchable 1.8V/3.3V GPIO, 3.3V I2C ODIO, and 3.3V Analog Cell

pull-down resistor. It has a sleep function which - when enabled - puts the I/O into an ultra-low power state and latches the I/O in the previous state. Cells for I/O, core power, and ground with built-in ESD circuitry are included. A power-on-control circuit is integrated into an available VDDIO cell. The GPIO can do TX and RX up to 150MHz. ESD targets are 2KV HBM / 500V CDM with 2KV IEC 61000-4-2 system stress capability.

View TSMC 22nm ULL Wirebond/Flipchip I/O Library with switchable 1.8V/3.3V GPIO, 3.3V I2C ODIO, and 3.3V Analog Cell full description to...

- see the entire TSMC 22nm ULL Wirebond/Flipchip I/O Library with switchable 1.8V/3.3V GPIO, 3.3V I2C ODIO, and 3.3V Analog Cell datasheet

- get in contact with TSMC 22nm ULL Wirebond/Flipchip I/O Library with switchable 1.8V/3.3V GPIO, 3.3V I2C ODIO, and 3.3V Analog Cell Supplier

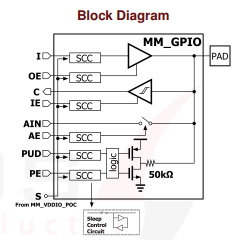

Block Diagram of the TSMC 22nm ULL Wirebond/Flipchip I/O Library with switchable 1.8V/3.3V GPIO, 3.3V I2C ODIO, and 3.3V Analog Cell

TSMC IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- Complete USB Type-C Power Delivery PHY, RTL, and Software