TSN Ethernet Switched Endpoint Controller

The controller core is designed to enable high-precision timing synchronization and flexible yet accurate traffic scheduling. With cut-through switching and minimal buffering even at the Ethernet MAC level, the TSN-SE features extremely low and deterministic ingress and egress latencies, and simplifies the development of time-aware applications. Furthermore, it allows the system to define and tune in real time the traffic shaping parameters according to an application’s requirements, and provides the system with timing information (time-stamps, alarms, etc.) that is typically required for the operation of a TSN network bridge or endpoint.

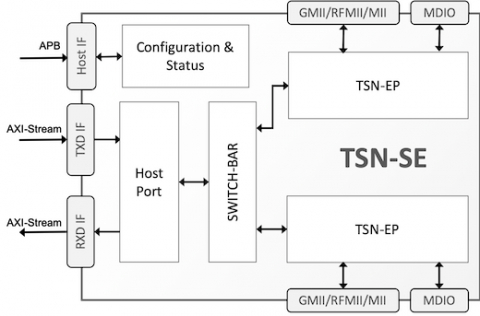

The TSN-SE uses standard AMBA® interfaces to ease integration. Its configuration and status registers are accessible via a 32-bit-wide APB bus, and packet data are input and output via AXI-Streaming interfaces with 32-bit data buses.

The TSN-SE is designed with industry best practices, and is available in synthesizable RTL (Verilog 2001) source code or as a targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

View TSN Ethernet Switched Endpoint Controller full description to...

- see the entire TSN Ethernet Switched Endpoint Controller datasheet

- get in contact with TSN Ethernet Switched Endpoint Controller Supplier

Block Diagram of the TSN Ethernet Switched Endpoint Controller IP Core

TSN Ethernet IP

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- TSN Ethernet Endpoint Controller

- TSN Ethernet Switch

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol IO Concentrator (RDC) IP Core for Safe and Secure Ethernet Network

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network