UCIe 2.0 PHY 4nm

View UCIe 2.0 PHY 4nm full description to...

- see the entire UCIe 2.0 PHY 4nm datasheet

- get in contact with UCIe 2.0 PHY 4nm Supplier

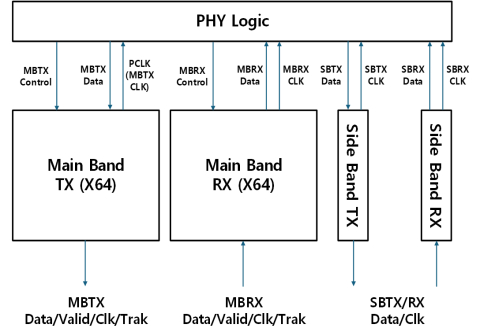

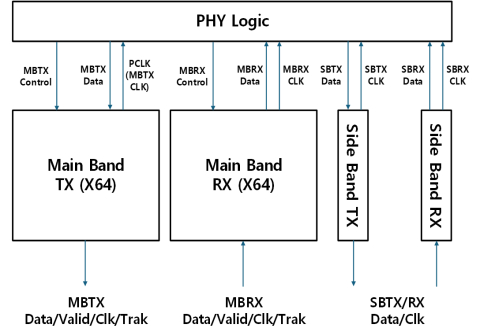

Block Diagram of the UCIe 2.0 PHY 4nm IP Core

Andes Technology Celebrates 20 Years with New Logo and Headquarters Expansion

Creonic Unveils Bold Rebrand to Drive Innovation in Communication Technologies

Beyond Limits: Unleashing the 10.7 Gbps LPDDR5X Subsystem

How to Design Secure SoCs: Essential Security Features for Digital Designers

What tamper detection IP brings to SoC designs

Design IP Market Increased by All-time-high: 20% in 2024!

What's Your Vector? Synopsys Introduces New ARC VPX6 Digital Signal Processor

Vision Transformers Have Already Overtaken CNNs: Here's Why and What's Needed for Best Performance

© 2024 Design And Reuse

All Rights Reserved.

No portion of this site may be copied, retransmitted, reposted, duplicated or otherwise used without the express written permission of Design And Reuse.