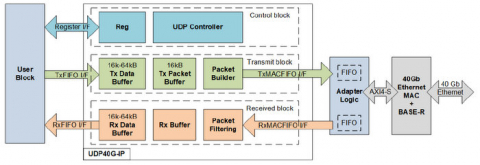

UDP40G-IP Core

User interface could be split into two groups, i.e. control signals and data signals. Control signals are designed by using general register interface while data signals are designed by using 256-bit general FIFO interface.

Register interface is used to set network parameters of UDP40G IP and the target device such as IP address and port number. Also, it is applied to start sending data operation and the control parameters for sending data such as transfer size and packet size.

Data interface of user logic is 256-bit FIFO interface for both Tx and Rx direction. User can design simple logic or connect to FIFO for connecting to UDP40G IP.

To initialize system, user needs to set up all network parameters of UDP40G IP and the target device, i.e. MAC address, port number, and IP address through register interface. After finishing initialization, UDP40G IP is ready to send or receive data with the target device. To send data, user sets command register and then transfer data to UDP40G IP until finishing. UDP40G IP creates UDP/IP packet which includes the user data and forwards to Ethernet MAC, following the parameters. Otherwise, when the new packet is received and the header in the packet is valid (matched to the parameters), UDP40G IP extracts only the data to return to user.

View UDP40G-IP Core full description to...

- see the entire UDP40G-IP Core datasheet

- get in contact with UDP40G-IP Core Supplier

Block Diagram of the UDP40G-IP Core IP Core