2.5D GPU / 2D & 3D Vector Graphics (OpenVG) Accelerator - D/AVE HD

UFS 3.1 Silicon Proven 2.1 Device, Host

Features

- Compliant with UFS Specification v2.x, 3.x

- Supports up to 2-lanes (restricted by Standard) running at HS-G3 (5.8Gbps)

- AXI Support

- All UPIU Processing

- Datain, Dataout, Command, Response, RTT, Query, Task Management and Reject

- Complete control of UIC Layer by UFS Host

- Error Reporting and Handling Supported

- Priority arbitration between command, query and task management UPIUs and Indexed based processing within Command and Query UPIUs.

- Supports 32 UTP Transfer request descriptors and 8 UTP Task Management Descriptors for UFS host

- Supports Boot LUN, RPMB Well-known LUNs.

- Device: Up to 8 LUNs configurable. Up to 8 command queue in each LUN. Up to 8 tasks handling for task management.

- Priority LUN handling.

- Security Features

View UFS 3.1 Silicon Proven 2.1 Device, Host full description to...

- see the entire UFS 3.1 Silicon Proven 2.1 Device, Host datasheet

- get in contact with UFS 3.1 Silicon Proven 2.1 Device, Host Supplier

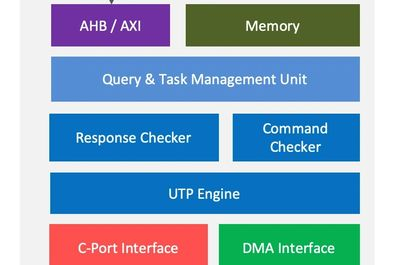

Block Diagram of the UFS 3.1 Silicon Proven 2.1 Device, Host IP Core

MIPI UFS Host IP

- UFS 4.0 Host Controller compatible with M-PHY 5.0 and UniPro 2.0

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- UFS 2.1 Host Controller compatible with M-PHY 3.1 and UniPro 1.6

- UFS 3.0 Host Controller compatible with M-PHY 4.0 and UniPro 1.8

- UFS Host 3.0 Prototyping Kit (HDK )Total IP in a Box

- UFS Host 2.1 Prototyping Kit (HDK )Total IP in a Box