Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz

With an ultra-compact footprint (0.008 sq mm), it is particularly suited for SoC designs that require precise phase synchronization across multiple clock domains. The delay resolution is as fine as 700 fs. Thanks to its adaptive dithering cancellation technique, it mitigates dithering issues, significantly enhancing jitter performance.

View Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz full description to...

- see the entire Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz datasheet

- get in contact with Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz Supplier

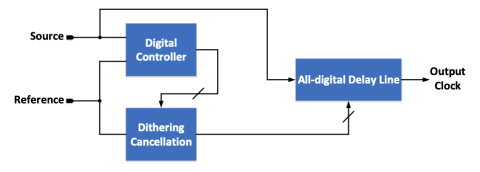

Block Diagram of the Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz

Low jitter IP

- TSMC GF Intel Low Phase Noise, High-performance Digital LC PLL

- Low jitter 4.96GHz to 5.6GHz PLL in TSMC N40

- PCIe/HCSL Differential IO Buffer - TSMC 16FFC

- Low jitter, low-power clock-deskew PLL operating from 6GHz to 9.5GHz

- Low jitter, ultra-low power (<950uW) ring-oscillator-based PLL-2.4GHz

- 25MHz Low Jitter Low Power XTAL Oscillator with AGC