USB 3.1 PHY (10G/5G) inTSMC (16nm, 12nm, N7, N6, N5,N3E, N3P)

USB 2.0 On-The-Go Controller

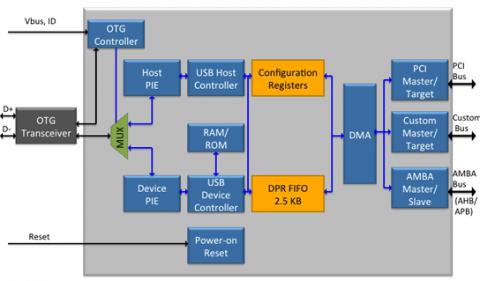

Session Request Protocol (SRP) and Host Negotiation Protocol (HNP) are managed by the SRP/HNP Control Logic. SRP allows a B-device to request an A-device to turn on Vbus to start a session. HNP allows two connected dual-role devices to change roles and eliminates the needs for the user to switch cable connections. The Vbus Control Circuit supports: a) the generation of data-line pulsing and Vbus pulsing methods when initiating the SRP as a Bdevice, b) the detection of both pulsing methods when acting as an A-device, and c) the sourcing of a minimum of 8 mA on Vbus. The Vbus Control Circuit also handles the pull-up and pull-down connections to D+ and D- during host/device role switching. The SRP/HNP Logic and Vbus Control Circuit control the operating mode of an USB port as either a host or peripheral. The Arasan USB 2.0 OTG port requires an external USB 2.0 transceiver with a standard UTMI interface.

The Arasan USB 2.0 OTG IP Core offers a high level of flexibility, allowing designers to implement the USB 2.0 OTG port with a wide selection of processor interfaces. AHB, PCI, and Custom buses are available to provide a high-speed connection to the USB interface.

The Arasan USB 2.0 OTG IP Core is augmented by the availability of the Arasan OTG Software Stack that supports host driver, device driver, class of devices, and Linux operating system.

View USB 2.0 On-The-Go Controller full description to...

- see the entire USB 2.0 On-The-Go Controller datasheet

- get in contact with USB 2.0 On-The-Go Controller Supplier

Block Diagram of the USB 2.0 On-The-Go Controller IP Core

USB OTG IP

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- USB 2.0 OTG On-The-Go Transceiver PHY

- USB 2.0 PHY IP, Silicon Proven in TSMC 22ULP

- USB 2.0 OTG High/Full/Low-Speed Dual Role Core