Ultra-low power 32 kHz RC oscillator designed in GlobalFoundries 22FDX

USB 3.0 Device Controller

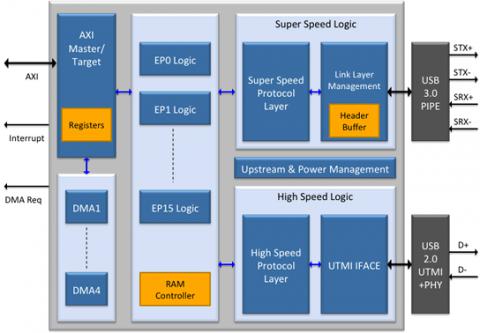

The USB 3.0 Device provides a dedicated dual simplex, routable packet architecture for USB3.0 and USB 2.0 packet transfers, giving the option to disable either for power savings. The USB 3.0 IP supports all power management features as well as a dedicated link manager for each downstream port for increased efficiency. It includes a high performance scatter gather DMA that can be configured to access any endpoint through registers. Optionally, it can interface with an external DMA controller. The Device IP core provides an UTMI/ULPI interface for USB 2.0 support and a PIPE interface for USB 3.0 support.

The USB 3.0 Host IP Core utilizes a flexible system bus architecture that can support AXI, AHB, OCP or any custom system interface needed for existing SoC development. The system bus can also be replaced with a dedicated FIFO interface to reduce bus bandwidth issues. The IP core includes RTL code, test scripts and a test environment for complete design verification.

View USB 3.0 Device Controller full description to...

- see the entire USB 3.0 Device Controller datasheet

- get in contact with USB 3.0 Device Controller Supplier

Block Diagram of the USB 3.0 Device Controller

Interface controllers and PHY IP

- Globalfoundries 12nm MIPI D-PHY V1.2@2.5GHz

- 1.6T Ultra Ethernet IP Solution with PHY, Controller and Verification IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- USB 2.0 PHY IP, Silicon Proven in UMC 40LP

- USB 2.0 PHY IP, Silicon Proven in UMC 28HPC