AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

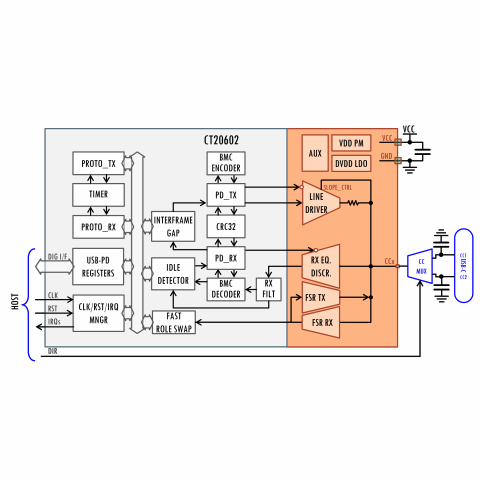

USB Power Delivery 3.1 Physical Layer

It also implements that part of the USB Power Delivery 3.1 Protocol Layer which are defined in the Type-C Port Controller specification, to simplify the integration with the Power Delivery Host Controller.

The Analog Front-End implements the slew-rate controlled transmitter block, the receiver block (fully compatible with the entire directives for line noise and cable DC offset and transients) and the Fast Role Swap transceiver.

The digital section of the PHY:

• Formats and sends messages

• Formats and sends signals

• Receives and validates messages

• Receives signals

• Detects incoming HardReset or CableReset signals

• Grants the inter-frame gap

• Supports SOP, SOP’ and SOP’’ and messages • Supports BMC BIST modes

• Receive and Send Fast Role Swap signal

CT20602 interfaces with the Host by means of a set of standardized registers which buffers USB-PD data packets and provides commands to control operations.

View USB Power Delivery 3.1 Physical Layer full description to...

- see the entire USB Power Delivery 3.1 Physical Layer datasheet

- get in contact with USB Power Delivery 3.1 Physical Layer Supplier

Block Diagram of the USB Power Delivery 3.1 Physical Layer IP Core