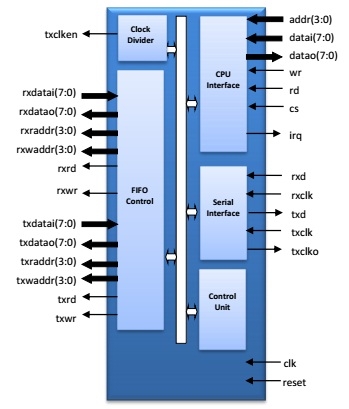

The DHDLC IP Core provides versatile support for a widely used HDLC transmission protocol. It manages the bit stuffing process, both address appending and detection. And if it’s not enough, let’s just mention that this Core supports CRC16 and CRC32 computation. Increased system performance and reduced CPU overload is a must be, thanks to the presence of separate receiver and transmitter FIFO buffers, maskable interrupt and DMA interface request. The DHDLC is a fully scalable IP Core, which makes it a perfect solution for both hi-end and deeply embedded projects. It’s tailored to your project needs and can be provided with: small 8-bit SRAM-like interface, 32-bit full AXI4 slave interface with burst support, AXI4Lite interface, AHB and APB slave interfaces. The optional Frame Status Buffer stores information about frames size and error conditions. Moreover, the size of the receiver and transmitter FIFO buffers is configurable. You can also easily remove unused features before the synthesis process. All that and much more make the DHDLC an ideal solution for very popular higher level protocol implementations like e.g. PPP (Point-to-Point), X.25, V.42, LAB-B, SDLC, ISDN and many others.