VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs

Features

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory and optional encoding mechanisms

- Backward compatible to DSC v1.1

- Configurable maximum display resolution up to 8K (FUHD)

- 8, 10, 12 bits per video component

- YCbCr and RGB video output format

- 4:4:4, 4:2:2, and 4:2:0 native coding

- Resilient to bitstream corruption

- 3 pixels / clock internal processing architecture in 4:4:4

- 6 pixels / clock internal processing architecture in 4:2:2 and 4:2:0

- Parameterizable number of parallel slice decoder instances (1, 2, 4, 8) to adapt to the capability of the technology and target display resolutions used

- Automatic run time configuration of the number of parallel slice decoder instances in use

- Support for Xilinx® 7 Series, UltraScale™, and UltraScale+™ FPGAs

- AXI-S interfaces for easy integration in the IP Vivado® integrator

- AXI-Lite interface for register access

- PPS 128 bytes block decoding

- Compliant solution for DisplayPort 1.4™ or HDMI® 2.1

- Compatibility for slices per line requirements

- Supports flexible usage models and design architecture (inline decoding or panel frame buffer decoding)

View VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs full description to...

- see the entire VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs datasheet

- get in contact with VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs Supplier

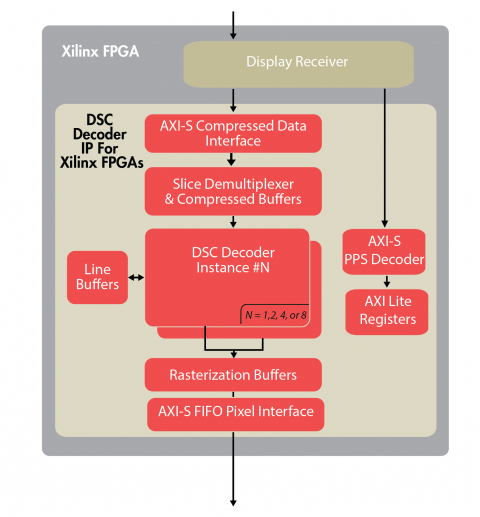

Block Diagram of the VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs

VESA DSC Decoder IP

- VESA DSC (Display Stream Compression) 1.2b Video Decoder

- ASIL-B Ready ISO 26262 Certified VESA DSC (Display Stream Compression) 1.1 Encoder

- VESA DSC 1.2b Encoder for Xilinx FPGAs

- VESA DSC Encoder and Decoder IP Solutions

- VESA Display Stream Compression (DSC) IP Core

- Display Stream Compression (DSC 1.2) Decoder