Voltage Optimization Modules

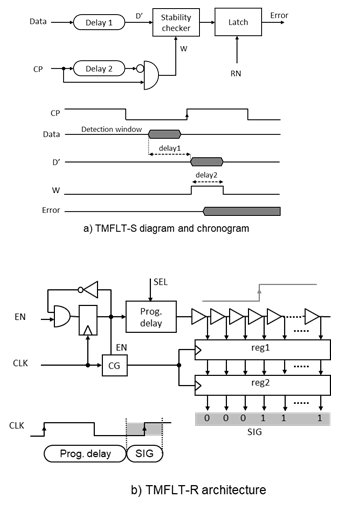

* TMFLT-S IP (Timing Fault Sensor)

Estimates the Fmax/Vmin of the circuit during a calibration phase

* TMFLT-R IP (Timing Fault Ring) :

Tracks either the minimum voltage operation (Vmin) or the maximum clock frequency (Fmax) during run-time phase

* TMFLT Sensor implementation methodology:

Allows choosing the best register candidates to insert TMFLT Sensors. Allowing to minimize the area overhead to less than 2%.

View Voltage Optimization Modules full description to...

- see the entire Voltage Optimization Modules datasheet

- get in contact with Voltage Optimization Modules Supplier

Block Diagram of the Voltage Optimization Modules IP Core

Voltage Optimization IP

- Low Noise, On-Die, Localized Voltage Regulation

- LDO Linear Voltage Regulator

- Dual Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 64 k

- Dual Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 64 k

- Two Port Register File compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 64 k

- Dual Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 72 k