Watchdog Timer with APB Interface

Via a 32-bit APB interface, the host processor can choose the timeout interval, enable, disable or clear the interrupt and reset lines, and pause or resume the timer. If the counter is enabled, it will decrement on every clock cycle. When the counter reaches zero, the interrupt output is asserted and the counter is reloaded with the timeout value. In case that the interrupt is not cleared before the counter reaches the zero value again, the output reset signal is asserted.

The core is designed so that the timer and the APB interface operate on different and unrelated clocks. This allows the timer to operate even when the rest of the system is in a low-power mode and bus clocks are not running.

Furthermore, to protect from unintentional configurations, write access to the core’s configuration registers is enabled only when a separate register, the “lock register”, holds a specific magic value. An attempt to write the core’s configuration registers while the core is locked (while the lock register does not hold the magic value) triggers a bus error.

The WDT-APB core is rigorously verified and available in RTL source or as a targeted FPGA netlist. Its deliverable includes a testbench, synthesis and simulation scripts and comprehensive user documentation.

View Watchdog Timer with APB Interface full description to...

- see the entire Watchdog Timer with APB Interface datasheet

- get in contact with Watchdog Timer with APB Interface Supplier

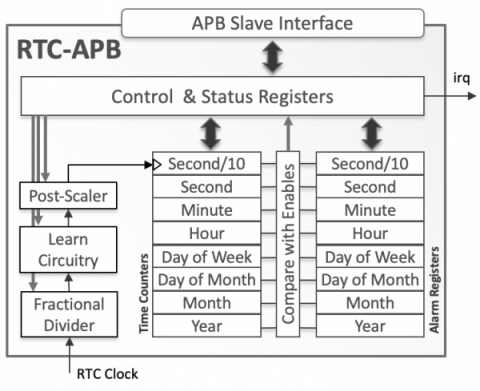

Block Diagram of the Watchdog Timer with APB Interface IP Core