RISC-V formal Verification IP

Formal verification produces exhaustive proofs of correctness and finds corner-case bugs in design implementations. The challenges with formal verification, however, are:

• Proof convergence is not guaranteed

• No consistency of formal coverage models across different formal verification tools.

• No consistency between formal coverage models and simulation

The formalISA® app addresses all these challenges successfully. Built on top of the first-generation ISA formal verification proof kit from Axiomise, the formalISA® app is powered by a clean graphical-user-interface that allows the end-user to push a few buttons to obtain formal verification results on a RISC-V core of their choice, using a formal verification tool of their choice. The push-button ‘ Prove’ & ‘Cover’ solution eliminates the need to:

• Write a single test case

• Write complex test sequences

• Write scoreboard or checkers

• Write constraints

• Randomize stimulus

View RISC-V formal Verification IP full description to...

- see the entire RISC-V formal Verification IP datasheet

- get in contact with RISC-V formal Verification IP Supplier

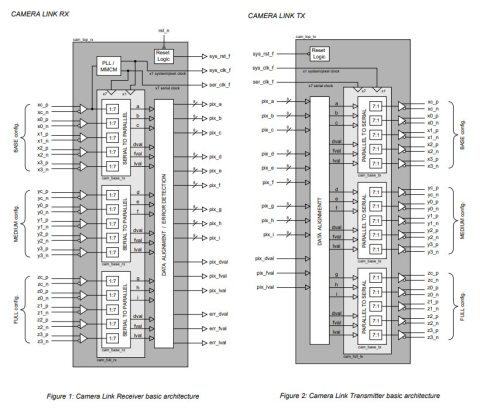

Block Diagram of the RISC-V formal Verification IP Verification IP