Simulation VIP for xSPI

The Cadence® Memory Model Verification IP (VIP) for xSPI provides verification of xSPI (Expanded SPI) NOR flash devices using the SPI protocol. The VIP for xSPI is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model. The VIP for xSPI includes both support for xSPI and VIP for OSPI NOR.

Supported specification: JEDEC specifications: JESD251 Profile 1 v1.0, JESD251-A1, JESD252, and JESD216D and Memory Vendors specifications of ADESTO (DS_XP032_114G_122018), MICRON (tn1235_sfdp_mt35x Rev. B 10/18 EN - compliant to JESD216B ONLY), MACRONIX, (AN0726 Rev1 for MX66UM2G45G) and CYPRESS (002-18216, Rev:*M).

View Simulation VIP for xSPI full description to...

- see the entire Simulation VIP for xSPI datasheet

- get in contact with Simulation VIP for xSPI Supplier

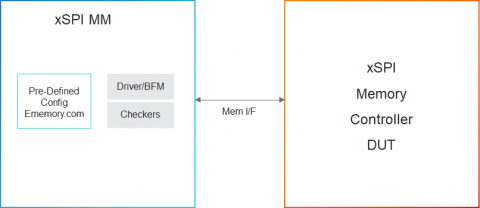

Block Diagram of the Simulation VIP for xSPI Verification IP