Jim Lipman, Director, Marketing, Sidense

Todd Humes, Vice President, Product Engineering, Sidense

For large amounts of on-chip code and data, mask read-only memory (ROM) provides an inexpensive and easily programmed storage mechanism. However, the inability to configure ROM after wafer processing means that information stored in the ROM cannot be changed in the field.

Antifuse one-time programmable (OTP) provides a flexible, field-programmable alternative to ROM. An antifuse-based bit cell uses controlled, irreversible thin (gate) oxide breakdown to program a bit. Un-programmed, the bit cell looks like a capacitor; but when the oxide is ruptured, there is a conductive path which exhibits current flow several orders of magnitude higher than that for an unprogrammed bit.

Antifuses program by applying a high-voltage pulse not encountered during normal operation across the gate and substrate of the thin oxide transistor (around 6V for a 2nm-thick oxide or 30MV/cm). This breaks down the oxide between gate and substrate. This programming voltage can be supplied externally or with an embedded charge pump. The positive voltage on the transistor's gate forms an inversion channel in the substrate below the gate, with the high electric field inducing a tunneling current to flow through the oxide. This current produces traps in the oxide, increasing the current through and, ultimately, melting the oxide, which then forms a conductive channel from gate to substrate. A current density of 100μA/100nm2 forms the conductive channel with the breakdown occurring in, typically, 100μs or less.

There are several reasons why field-programmable OTP makes sense. First, the chip designer can commit to silicon prior to code completion. This feature accelerates product time-to-market. The flexibility of being able to try different versions of chip code and to perform side-by-side comparisons of the code versions allows software developers to optimize code for a particular design. Finally, field-programmable OTP also supports a chip design that can have additional features that may not be available on initial silicon, but can be added in later versions of the chip.

One chip can also have several variants, which simplifies inventory and allows a single chip to support multiple versions of a feature set. This is useful, for example, in an application such as an entertainment system for an automobile family where different car models within that family have different levels of audio requirements. Another example would be implementing a chip supporting several communications protocols such as a network chip supporting Bluetooth and Wi-Fi. In a given application, the chip is enabled to support either one or both of these protocols using antifuse-based OTP in place of ROM to do the specific enablement.

When investigating embedded field-programmable OTP for a chip design, be aware that different products (having different bit cell architectures) on the market have varying characteristics, as is the case for any embedded memory intellectual property (IP). The best antifuse OTP architecture provides memory IP that is very dense, has a fast read access time, and supports easy conversion from the OTP macro to mask ROM for cost reduction during production.

1T vs. 2T Antifuse OTP Bit Cell

There are two basic oxide breakdown antifuse OTP architectures available – two transistors (2T) per bit cell and one transistor (1T) per bit cell.

An inherent problem with a 2T antifuse bit cell is predicting where the conductive programming channel will be located. Three potential regions exist where the oxide breakdown occurs: above the transistor channel, to a leakage control implantation or to the lightly doped drain (LDD) diffusion. This variability compromises the reliability, yield and portability between processing facilities of arrays using the 2T antifuse bit cell since the bit cell read and programming characteristics vary between these different regions.

A split channel (1T) metal oxide semiconductor (MOS) antifuse bit cell eliminates the diffusion area from the thin oxide transistor, ensuring programming in the normal transistor channel region. This produces a bit cell exhibiting more consistent programming and read characteristics. In addition, the 1T bit cell, not much larger than a mask ROM bit cell, consumes significantly smaller area than a 2T bit cell. This area reduction increases overall chip yield and decreases cost, particularly for large memory blocks. Furthermore, a 1T bit cell exhibits very fast read access times, as low as 10ns for advanced process nodes, ports more readily between foundries and scales easily with process node shrinks.

Figure 1. Split Channel Antifuse-based OTP Bit Cell

The 1T split channel antifuse-based OTP bit cell has several advantages over a 2T bit cell, which makes the 1T architecture a more viable candidate for ROM replacement.

OTP vs. ROM

Using 1T antifuse OTP in place of ROM does require slightly more area. In addition, the programming time OTP requires increases approximately linearly with bit count. While ROM is programmed during chip fabrication, there is no programming time or cost; however, the ROM still needs to be tested to verify its contents. While these OTP considerations are not very important for small bit count applications, they are at high bit counts, for example, when the OTP is storing hundreds of thousands of bits of boot code or firmware. Programming and verifying OTP will result in additional test time.

These OTP factors are acceptable at a prototype phase of chip development, but may become too expensive during production, especially for high bit count applications. However, the ability to complete code development during silicon fabrication and make and test code changes during prototyping, coupled with the ability to accelerate market entry and reduce final product cost, provides a compelling argument for using field-programmable OTP during product development.

ROM Conversion

Designers need to consider the ease of converting the OTP macro to ROM when evaluating an antifuse-based OTP memory architecture.

For some OTP architectures, conversion to mask ROM requires a single graphic data system (GDS) layer change—diffusion (thin gate oxide)—within a standard process flow. Many customers do their prototype development using multi-project mask sets to cost-share the mask set with other developers. When they go into production, they then purchase a production-quality mask set anyway, so they do not incur any incremental costs of this layer change. Accelerating product time-to-market often justifies the added mask cost for changing to ROM should a customer already use a dedicated mask set while providing a cost-reduction path.

Figure 2. Split Channel OTP to Mask ROM Conversion

A split channel antifuse OTP bit cell supports a very simple conversion to mask ROM, with only a single GDS layer change (for diffusion) and no variations from a standard process flow.

There are many benefits of converting either all or part of an OTP macro to mask ROM once all or part of the bit storage is frozen. First, there is significant cost savings due to the reduced time for automatic test equipment (ATE) programming of the macro. The memory footprint does not change when converting field-programmable 1T OTP to mask ROM, minimizing non-recurring engineering (NRE) costs for layout.

With a 1T bit cell architecture, designers may "mix and match" OTP and ROM in the same macro for many applications, such as factory or field trimming of analog circuitry and sensor conditioning; product customization (one silicon chip with several variants) where functionality is enabled by OTP programming; chip identification, lot date coding and other identification functions; future code patching; and end-customer personalization such as that required for digital hearing aids and implanted medical devices.

Security Considerations

An additional advantage of antifuse OTP in place of ROM is the extra security it provides for stored data or code. Reverse engineering (via de-processing) a ROM bit will easily determine whether the memory cell is storing a 1 or a 0. It is virtually impossible to determine the content of an antifuse OTP bit cell, either by physical de-processing or by voltage scanning after removing the top layers of the chip. Since the antifuse bit cell does not use stored charge to determine whether it contains a logical 1 or 0, scanning the cell will not reveal its contents.

If a memory macro contains both ROM and antifuse OTP, creating an encryption key in OTP for decrypting the ROM will help assure security of the ROM's contents since the key is inherently secure.

Example

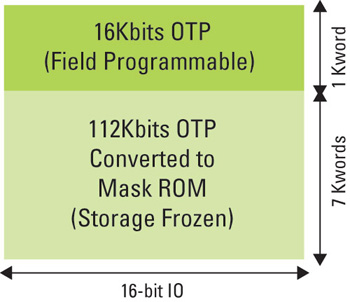

The following example shows a 128Kbit (8K x 16) OTP macro used for storing code. 112Kbits of code storage have been finalized and the macro section with this stored code converted to ROM. The remaining 16Kbits of field-programmable OTP are reserved for future code development by the end-product manufacturer. After the ROM conversion, the programming time for this macro is reduced by 87.5 percent.

Figure 3. Partial Conversion of an OTP Array to ROM

The ability to convert part of an antifuse OTP array to ROM substantially reduces ATE time and cost for arrays programmed during test while leaving some field-programmable memory for future trimming, chip ID, code updates or other purposes.

About the Authors

Jim Lipman is currently director of marketing at memory IP provider Sidense. Prior to Sidense, Jim worked at Cain Communications as vice president of client services, TechOnLine as content director, and at EDN Magazine as application-specific IC (ASIC) and electronic design automation (EDA) editor. He also was employed by VLSI Technology, where he held various training, marketing and public relations positions, and did chip designs at both Hewlett-Packard and Texas Instruments earlier in his career. Jim received his B.S.E.E. and M.S.E.E. degrees from Carnegie-Mellon University in Pittsburgh, Pennsylvania and his doctorate in electrical engineering from Southern Methodist University in Dallas, Texas. He also has a Masters of Business Administration from Golden Gate University in San Francisco, California. Jim is a senior member of the IEEE. You can reach Jim Lipman at 925-606-1370 or jim@sidense.com.

Todd Humes brings over 20 years of engineering and management experience to Sidense, where he is the vice president of product engineering. Following the acquisition of Impinj's IP group, he was senior director of engineering at Virage Logic for the embedded NVM group. Prior to working at Virage Logic, Mr. Humes joined Impinj at its inception and served as chief technical officer and, later, vice president of engineering for IP products. Mr. Humes was also responsible for Impinj's patenting efforts. Before Impinj, he held several management and engineering positions at TRW. Mr. Humes earned his M.S. in electrical engineering from the California Institute of Technology and B.S. in electrical engineering from California Polytechnic State University, San Luis Obispo, California. He currently holds 39 United States patents and has numerous U.S. and foreign patent applications. You can reach Todd Humes at 206-719-5361 or thumes@sidense.com.