Flavio Castro, Universidade de Pernambuco, Recife Brasil

Abstract :

This paper describes the design and implementation of a version of the 8051 microcontroller, one of the most commercially used microcontrollers in FPGA with reconfigurable instruction set.

Reconfigurable systems offer a solution to solve complex problems by combining the speed of hardware with the flexibility of software to improve performance and system performance [1].

The aim of this paper is to present the development of a simplified version of the 8051 microcontroller combining the technical configuration of the set of instructions executed in development time and the same dynamic reconfiguration at runtime. The microcontroller uses proposed more than a fixed set of instructions, with only one active at any given time and provide the ability to create new combination of instructions so that the microcontroller can incorporate them and use them in real time as if they were part of the fixed set of instructions.

In this work comparative simulations are presented in relation to the time of execution and performance of traditional systems in relation to the microcontroller developed.

In future work we intend to use this "core" with instructions on reconfigurable network of embedded processors in SOC (system on chip) facing the staggering task.

1. INTRODUCTION

In recent years we have witnessed the growth of embedded systems design and telecommunications, which are mostly based on microcontrollers.

Microcontrollers have features of a full computer system on a single chip, supporting activities of data acquisition, processing and control devices in industries and in complex projects involving electronics and computer [2].

However the complexity of these devices has grown more and more the need for devices with better performance, flexibility to changing customer requirements, ability to adapt to operational changes and cost to ensure the competitiveness of new products [3].

The technological advances of programmable devices such as Field Programmable Gate Array (FPGA), allowed to design and develop high-performance digital systems and capable of reconfiguring the hardware in order to optimize the features required to systems and control paradigms of the application [4].

2. CONTEXTUALIZATION

2.1 Reconfigurable Systems

Many emerging applications in telecommunications and multimedia require flexibility even when implemented in view of the mutability patterns in the characteristics of systems and protocols during the life of equipment.

There are two paradigms for solving these problems are fixed hardware solutions (HF) and solutions in software-programmable hardware (HP + W).

The HF solutions based are faster, but they are expensive and are not flexible because it does not allow you to change their characteristics after manufacture. Since the solutions based on software components are flexible, allow to easily correct mistakes and reuse components, but provide less than optimal performance and consume more power.

An intermediate solution between these two paradigms are reconfigurable devices.

The systems are reconfigurable hardware platforms with the ability to modify itself by software to better suit the application. Thus we have two basic types of reconfiguration:

a. Static reconfiguration, when the reconfiguration occurs in the development phase.

b. Dynamic Reconfiguration and / or Partial reconfiguration and when performed at runtime.

A reconfigurable architecture can also be hybrid, when they have a piece of hardware fixed and a reconfigurable, thus enabling even greater flexibility [5].

FPGAs are programmable circuits composed of a set of logic cells placed in the form of a matrix as shown in Fig.1. The logical structure varies from each manufacturer, but kept the main elements are: Configurable Logic Block (CLB) which is the logical unit of the FPGA, In / Out Block (IOB) that are responsible for the FPGA interfaces with the external environment and Switch Box (SB) which is the element responsible for the interconnection between the CLB routing through channels [2].

Figure 1. Component elements of the FPGA

The field of reconfigurable computing has advanced extensively in the last decade using FPGAs as the basis for high performance reprogrammable systems. Many of these systems have achieved high levels of performance and demonstrated its applicability to solving a wide variety of problems [6].

A hardware description language describes what a system does and how it does. One of the most used languages in the description of hardware is the VHSIC Hardware Description Language (VHDL).

A system described in language can be implemented in hardware allowing the use of FPGA in the field of your system, taking advantage of the code change at any time [7].

2.2 Microcontroller 8051

The Microcontrollers are devices with features of a computer system on a single chip, RAM, EPROM memory, Central Processing Unit (CPU), communication ports I / O software selectable, block communication with any known protocol, timer generator signals for switching analog / digital converter and other characteristics of the manufacturer. In Fig.2 we have the architectural model of a microcontroller basics.

The Microcontroller 8051 is one of the most popular microcontrollers in the market. It is a simple 8-bit microcontroller, which can be found as a key element in the various equipment and systems.

Figure 2. Basic Architecture of a microcontroller

The microcontroller 8051 is a CISC (Complex Instruction Set Computer) it has about 100 instructions and uses a typical 12MHZ clock.

Microcontrollers are general purpose devices and in view of the requirements of modern systems for the speed, performance and fault tolerance, the time spent searching and instruction decoding is a bottleneck, because it directly influences the performance for solutions conventional microcontroller [8].

To resolve this issue were developed versions of the 8051 microcontroller on FPGA, using the properties and seeking to rewrite the necessary features that optimize applications.

2.3 Integration between the Microcontroller 8051 and FPGA

Currently there are commercial implementations of FPGA microcontroller 8051, focused on the processing of discrete tasks, with fixed set of instructions that cannot be modified to adapt to new situations processing. Some "core" of these are free and others as owners of Oregano mc8051, which provides all the components and peripherals of the microcontroller 8051 standard [5].

3. PROPOSED MODEL

Our proposal is to build an 8051 microcontroller with FPGA dynamic reconfiguration of instruction, which may alter during the running time and a fixed instruction set implemented by means of fixed hardware development time.

The creation and combination of the statements are made through a reconfiguration unit RFU (Reconfigurable Functional Unit) processor built into the microcontroller. This unit allows you to send customized instructions to the processor and then use them as instructions fixed as shown in Fig.3.

This form of coupling is limited space available on the processor. The RFU could also be attached as an external drive attached via the main bus.

Figure 3. Microcontroller Architecture Proposed

The processor will operate in two modes: reconfiguration mode and run mode. To start the reconfiguration process requires the user to send an external signal to the processor telling you that want to reconfigure the instruction.

The control unit will be implemented in the form of a finite state machine. The model validation will be accomplished through four sets of simple instructions with different characteristics in order to be able to switch them during operation. The instruction sets are composed of common general purpose instructions and one specific. In addition have the ability to create new instructions.

In the design of reconfigurable logic was considered among other things the amount of internal instructions and type of instructions provide maximum performance. Is shown in Fig.4 the basic structure of the RFU.

Figure 4 . Structure of a RFU

If segments are used, the configuration of an instruction is done in a hierarchical manner. The instruction is assigned a set of segments, and inside those segments, the processing elements are configured [10].

4. PRELIMINARY RESULTS

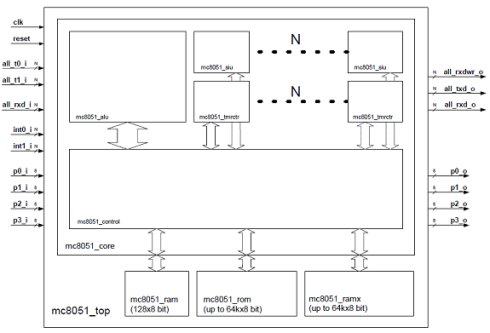

Initial tests of the controller is performed using the QUARTUS II version 11. The basis of the 8051 microcontroller core that will be used will be an open core business, such as mc8051of oregano as Fig.5, which incorporates the basic features of standard microcontroller. It will be used only a subset of the 8051 simplified instructions. Starting this core basics are all structured the architecture and functional blocks.

Figure 5. Block diagram of the 8051 microcontroller IP-core Oregano

Preliminary results of simulations were satisfactory and show a performance improvement over traditional solutions for core instruction set to fixed. However with the results available is not yet possible to quantify the levels of improvement shown. The main difficulty encountered so far is the definition of fixed sets of instructions. Each set of features and instruction set has its own instructions, but instructions are common to the four sets. Each instruction can be classified in various ways such as the time of execution, pipelining and internal state. If the type of reconfigurable instructions closely resembles the instructions supported by the fixed microprocessor, the integration process will be easier.

The last step will be to conduct tests using a development kit from Altera Cyclone II FPGA Starter Development, with the following features: 8MB SDRAM, 512KB SRAM, 4MB Flash, audio codec.

5. CONCLUSIONS AND FUTURE WORK

In future work we intend to continue this same line of research and enhance the use of the core with reconfigurable instruction set processors for networked embedded in SOC capable of scheduling tasks. Furthermore you can optimize the instruction sets of fixed to better adapt to a wide range of different applications, allowing it to that use of the core is enhanced.

6. REFERENCES

[1] ZAQUEU, J.P.B and ESKINAZI, R. 2011. Implementação de uma versão Harvard/RISC reconfigurável do microcontrolador 8051 em FPGA. In IBERCHIP 2011.

[2] ORDONEZ, E.D.M., PEREIRA, FD.., PENTEADO, C.G. and PERICINI, R.A. 2003. Projeto, Desempenho e Aplicações de Sistemas Digitais em Circuitos Programáveis (FPGA). São Paulo: Bless.

[3] KOJIMA,L. 2007. Metodologia de Projeto de Sistemas Dinamicamente Reconfiguráveis. Tese de Mestrado, Escola Politécnica da Universidade de São Paulo, São Paulo.

[4] JARA, M.A.R. 2010. Desenvolvimento de um Sistema Dinamicamente Reconfigurável baseado em redes intra-chip e ferramentas para posicionamento de módulos. Tese de Mestrado, Escola Politécnica da Universidade de São Paulo, São Paulo.

[5] CASSILO, L.A. 2005. Projeto e implementação em FPGA de um processador com conjunto de Instrução reconfigurável utilizando VHDL. Tese de Mestrado, Universidade Federal do Rio Grande do Norte, Natal.

[6] ESKINAZI, R. 2006. Uma Metodologia Para Escalonamento de Tarefas de Tempo Real em Arquiteturas Dinamicamente Reconfiguráveis. Tese de Doutorado, Universidade Federal de Pernambuco, Recife.

[7] MESQUITA, D.G. 2002. Contribuições para reconfiguração parcial, remota e dinâmica de FPGA. Tese de Mestrado, PontifÃcia Universidade Católica do Rio Grande do Sul, Porto Alegre.

[8] ORNONEZ, E.D.M., PENTEADO, C.G and SILVA, A.C.R. 2006. Microcontroladores e FPGA: Aplicações em Automação. São Paulo: NOVATEC.

[9] CARDIM, M.H.C. 2005. RTRASSOC51 – Módulo de Pipeline para um processador com arquitetura Harvard Superescalar embarcado (PAHSE).Tese de Mestrado, Fundação de Ensino EurÃpedes Soares da Rocha, São Paulo.

[10] BARAT, F. and LAUWEREINS, R. Reconfigurable Instruction Set Processors: A Survey. in IEEE 2000.