Mohit Gupta, IP Manager, Open-Silicon Inc.

Milpitas, California, US

Abstract:

3rd Party IP has become a buzz word since the Semiconductor industry has shifted gears to Fab-lite and eventually to Design-lite models in last few years. The new business models have opened the doors in many companies to overcome some of the internal weakness about possessing any IPs/design competencies to do a next generation ASIC/SoC designs. There have been multiple debates about which and to what extent should a company look into 3rd party IP. This paper outlines some best practices for using the ecosystem as well as some of the common challenges in integrating and using 3rd Party IPs in today’s high-end ASIC/SoCs.

3RD PARTY IP MARKET

The strategy of using 3rd Party IP ecosystem has been very successful when one considers the advantages of licensing the IPs from outside world:

- Better Time to Market: Using readily available IP can help kick start the chip design and will ultimately lead to shorter design cycles.

- Lower Cost: Applying generic foundation IP like Standard Cells, General Purpose I/O libraries and Memory Compilers will often be cheaper as compared to the costs associated with internal IP development, verification and (test-chip) characterization.

- Increased Focus: Companies can focus their R&D efforts on their differentiating technology, rather than spending their resources on designing IP, which often is standards-based and provides minimal differentiation to the end product.

- Reduced Risk: IP vendors are likely to be early adopters of newer technologies and typically qualify the IP on their own test chip or in collaboration with a lead customer.

Of course, one can argue that this approach has some disadvantages as well:

- Specification Compromise: “Off-the-shelf†open-market IP can never be fully optimized for all possible product applications. This provides a major challenge where criteria like area, performance and features may need to be traded off against aspects like cost, risk and time-to-market. Sometimes an in-between solution where available IP is customized by the vendor towards the customer-specific application can make sense however.

- No Ownership of IP: IP licenses come with various restrictions which can “get in the wayâ€. Examples are: re-use, disclosure and modification rights limitations which can possibly impair a company’s flexibility if not taken into account well in advance.

Looking at both pros and cons, at a system company it probably makes the most sense to focus only on the development of IPs in-house which differentiates a product rather doing everything on its own. For example; for a baseband chip, it is utmost important to do the Processor architecture and Hardening, RF system, Power management blocks etc. in-house as that will differentiate their products from their competitors in market rather than spending effort on generic IPs like USB, MIPI, HDMI interfaces, libraries, GPIOs etc. which are easily available in outside world and probably already silicon proven on IP vendors testchip.

Integration of 3rd Party IPs:

Procuring IP from third-party IP vendors looks to be a good option, but selecting and integrating that IP is rapidly becoming one of the biggest challenges in the SoC/ASIC industry. The success of any design depends on the careful selection of reliable IP which sufficiently meets the product’s requirements. Today, a significant portion of metal re-spins or redesign of chips is due to the fact that either the IP is not properly selected, or it has a bug inside, or it is not properly integrated into the design.

It is very common for IP to be procured from multiple vendors for a single design. Working with each vendor requires careful management of technical, quality, business and legal issues. Taking hard-IP as an example, modern SoCs often integrate multiple high-speed serial interfaces, such as PCIe, USB, and XAUI; memory interfaces such as DDR; CPUs such as ARM, MIPS, and Tensilica; analog IP, including ADCs, DACs, PLLs, DLLs; and power management blocks, next to library and commodity IP that includes memories, I/Os, and standard cells.

Fig 1. Typical SoC Components

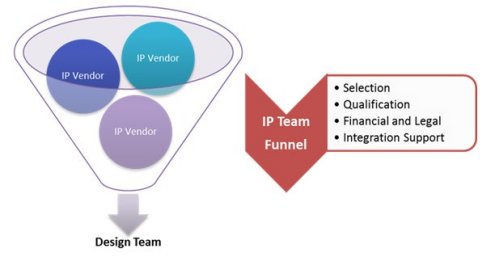

For each component in a SoC, there are specialized IP vendors with proven track records providing the IP in the whole ecosystem. Though there are many benefits to have multiple sources in the market at the same time it brings challenges for IP integration. To combat this, an IP selection and qualification process is needed. This process needs to be exhaustive and comprehensive and cover each phase of the ASIC design, from specification to GDSII.

Even a small oversight, such as realizing late in the tapeout phase that one of the IPs uses LVt devices where only RVt devices had been budgeted for can have major impact on cost and schedule. A seemingly small mistake made in the due-diligence stage as performed early in the ASIC development cycle, can lead to excessive costs down the road when the issue is encountered.

Fig 2. 3rd Party IP Use Process

The figure above shows a comprehensive 4-stage IP Selection, Procurement, Qualification and Integration process, starting from day one when the project is still in the specification phase. Understanding customer requirements (or sometimes even driving them), selecting the right vendors, the right IP, conducting IP risk assessment and mitigation, as well as performing qualification and integration checks, are integral parts of any Project. Each of these steps is composed of various checks and analysis in order to assure one thing: The right IP is being used in the right manner!

Each part of the above process in Fig 2 is quite rigorous in itself and requires great amount of effort by the IP Procurement and Integration team.

IP and Vendor Selection process is the most important and foundation step for the whole design. Taking shortcuts during this process will no doubt increase the chances of failures at later stages. This process encompasses matching the IP requirements as per the design needs, finding the right vendors and making sure that the 3rd Party IP serves all those needs required for the particular design.

Also, for the various IPs being procured both compatibility and interoperability need to be insured. For example, in TSMC's 40G process, multiple voltages can be supported for the I/O oxide (1.8, 2.5 and 3.3V). However, not all combinations are supported at this technology node. The selection of different I/O libraries and PHYs needs to take this into account to ensure compatibility of the selected IP. Another example involves DDR PHYs and its associated controllers. Interoperability concerns can exist, especially in cases where the DDR and the PHY are procured from different vendors, as the standard for the interface between them is new and may, to a large extent, still be unproven.

Fig 3. IP Aggregation in a Design

IP Procurement is the next important step after all the IP and vendors have been finalized for a design. This process involves financial, legal, schedule and various other contracts/agreements and negotiations with the vendors.

One other important aspect while procuring the IP from an external vendor is the assessment of views and models delivered by the vendor which will be used with the existing ASIC semi-custom/full custom design flow.

There have been efforts by bodies like IP-XACT to standardize the IPs in a way of their definitions but still due to various EDA flows, tool choices due to historical reasons etc., an IP delivered by multiple IP vendors may not look same. It might require generation of some auxiliary views like IBIS views for IOs from spice, milkyway databases, and characterization at custom corners for analysis etc. which might not be available from an IP vendor as a default delivery option.

IP Qualification: Third step is the IP Qualification step which incorporates an exhaustive incoming IP inspection process that helps in finding any issues with the IP very early in the project design cycle. This approach provides lead-time for the IP vendor to fix any issues upfront, which might show up in the ASIC tape-out phase of the project. This process is required for the same reason most of these steps are in place, the later a bug or an issue involving IP is caught, the more costly fixing it becomes.

IP inspection encompasses checking the IP within itself and with the other IPs in the ASIC. When checking the IP within itself, it is important to perform checks related to IP compatibility with the technology process node selected in terms of mask layers, gate oxides etc. and IP compatibility with the used design flow.

Checking the contents of IP delivery in terms of views completeness is another area that often gets missed. An agreement with an IP vendor might only cover basic views for the RTL to GDSII flow but there can be a requirement of specific views like IBIS models for IO libraries to do system level simulations.

Fig 4. IP Qualification Process

These might come at additional time and cost. Also, there can be the case of an IP view/model having been generated using a flow from one EDA vendor, where it may not seamlessly work with another. Issues like these have the potential to negatively impact the project if not identified early.

Fig 5. Relative Cost of fixing IP with design cycle

IP Integration is the last step in the chain though it pretty much runs throughout the program until the tapeout. This step is one of the areas which is constantly evolving. When new IPs/vendors are used in a design this process becomes more tedious. To tackle this task, various IP checklists and integration reviews should be deployed. These should be updated regularly to make sure all the aspects of Integration like Timing, DFT, Physical Design, Package are addressed for each IP. These checklists should carry a lot of know-how from the experience of the other design in terms of best practices and recommendations based on the silicon performance.

There are various requirements that each IP vendor provides on how to use the IP—should these requirements not be met, the successful IP integration may be hampered. Also, as part of the process IP vendors should do the final reviews and make sure that it satisfies all the requirements. One area that requires attention when managing multiple IP vendors is the understanding of ESD compliance for the entire chip. IP vendors will guarantee ESD targets only for their individual IPs and have tested ESD compliance for the IPs only in their own testchip environment. IP integration should incorporate specific ESD reviews and analysis for the various IPs integrated on a design to mitigate this risk during the Physical Design phase of the project. Overall with this process there should be significant savings for the companies in terms of last-minute ECOs and metal re-spins by catching some of the issues very early on in the process.

Summary:

Achieving a first-time-right SoC design depends greatly on IP Selection, Procurement, Qualification and Integration processes and methodologies. Ensuring that the IP as used in the SoC will ultimately meet all requirements is a highly complex task that requires a dedicated, expert team with an explicit focus and responsibility to this task. At Open-Silicon, we have a dedicated IP Application Engineering team which is responsible for taking care of the whole process described in this paper. Open-Silicon’s IP experts work continuously with customers and IP vendors to make sure all the requirements are met and IPs are successfully integrated in the design.