Jim Lipman, Sidense Corp.

Introduction

It is already a cliché to say that power is the new timing, but that doesn’t mean that it isn’t true. Two huge markets for chips are mobile and data centers. Although mobile is battery-powered and data centers are tethered, both have enormous pressures to keep power down.

Power is important in mobile because the end-user really cares about battery life and won’t buy products where it is too short. Another consideration is that if the power is excessive, the mobile device gets too hot to hold. This is obviously most severe with smaller devices such as smartphones that have a lot packed into a small volume.

Qualcomm has a famous video, the butter benchmark, where different cell phones are used to melt butter to dramatically illustrate their power dissipation.

Data centers have two power issues. First, power limits the clock-frequency for chips in servers, routers, disk drives and so on, because the chips would just get too hot and malfunction. Several years ago Intel’s then CTO famously predicted we were on course to power densities only found in nuclear reactors and rocket nozzles. Secondly, overall power from all the equipment is a huge part of the total cost of ownership of a data center, comprising the electricity to power the racks and to power the cooling infrastructure to dispose of the waste heat.

A New York Times article (Power, Pollution and the Internet) published September 22, 2012 states that, “Worldwide, the digital warehouses [data centers] use about 30 billion watts of electricity, roughly equivalent to the output of 30 nuclear power plants, according to estimates industry experts compiled for the The Times. Data centers in the United States account for one-quarter to one-third of that load, the estimates show.â€

The problems are not getting any easier. We all want more functionality in our phones, new wireless standards mandate higher bandwidths and data centers have to process more data. But the overall power budget cannot increase since the battery has to last as long (and can’t get any bigger) and data center power can creep up at best just a tiny amount.

The Need for OTP

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP on-chip. The data can be held off-chip in some sort of programmable memory (or, perhaps, ROM). But this obviously has the disadvantage of requiring the cost of an extra chip. In smartphones it is not just the cost of another chip that is a problem, but the additional volume taken up by two chips. There is just not a lot of room inside a smartphone to fit everything.

Another alternative to OTP memory is flash memory. This has a big advantage, which is that a flash memory can be reprogrammed many times. However, this comes with a big disadvantage in terms of added process complexity and, thus, the cost of the silicon. Even when off-chip flash memory already exists, security reasons may make using it for holding critical data impractical and running code out of flash memory may, in fact, require data from the flash to be copied to SRAM on the chip, which is both an added cost and yet another increase of unwanted power.

OTP memory has the advantage that code can be executed in-place and does not need to be copied from external memory into on-chip SRAM. It is fast enough and with low enough power as to make copying data out to SRAM something that is unnecessary.

Sidense 1T-OTP

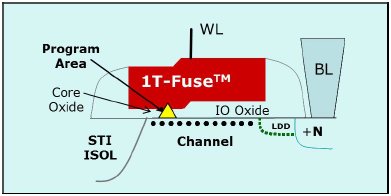

The Sidense one-transistor OTP (1T-OTP) architecture is especially area efficient since it uses a single transistor per bit cell. Furthermore, it does not depend on charge storage and so once programmed, it cannot be un-programmed by environmental or electrical upsets. The patented Sidense 1T-Fuse™ antifuse technology works by permanently rupturing the gate-oxide under the bit-cell’s storage transistor in a controlled fashion, obviously something irreversible.

Another big advantage of the Sidense antifuse approach is that it uses an unmodified digital process. No additional masks or process steps are required, so nothing is added to the wafer manufacturing cost. The per-chip cost rises due to the area occupied by the OTP, but since the 1T-OTP macros are very area-efficient this increase is usually very small. Additionally if the 1T-OTP is programmed at the tester, the increase in test time will also result in some extra cost.

The Sidense 1T-OTP memory uses a low read voltage, which further keeps the power of the memory down. The Sidense memory does require some non-standard voltages internally, especially during programming, but these are created using embedded charge pumps and are hidden from the user. The OTP memory can simply be hooked up to the chip’s power supply network just like any other memory block.

Another option to the Sidense solution to lower the power even more is to use differential bit storage. This technique requires each bit of information to be represented using two transistors: one 0 and one 1. This makes sensing the state simpler and as a result the voltage required for the memory can be lower still, along with the associated power. Obviously this comes at the cost of an increase in area since the number of transistors required to represent a given amount of data is doubled within the memory macro.

In high security applications, this differential signaling approach makes the data in the memory impossible to deduce by certain techniques that involve monitoring very minor fluctuations in the power absorbed by the chip. Since every read involves both a 0 cell and a 1 cell, the contents of individual bit cells cannot be determined by a power signature analysis. The Sidense approach is also inherently very secure against reverse engineering approaches. Even removal of chip layers and staining cannot detect the difference between a 0 value and a 1 value, since a programmed channel through the oxide underneath the bit-cell gate is virtually impossible to detect, even with an electron microscope.

Some applications require “few-time†programmable memories, for example to update encryption keys or program code, which may happen just a few times over the relatively short lifetime of a device like a smartphone. The Sidense memory can mimic this by expanding the memory core to the number of programming occurrences desired (emulated Multi-time Programmable, or eMTP). To update the memory, a new block is programmed and the latest programmed value is then read. This is clearly more appropriate for smaller memories than larger ones since the area overhead for the extra bits is relatively small.

Many power-sensitive designs, which means pretty much all of them, have a need for OTP memories. Sidense’s 1T-OTP solution is especially well suited for these applications since:

- It uses a standard CMOS process without extra masks or processing steps

- The one transistor bit-cell design minimizes area, power and overall chip cost

- A differential read mode can further reduce power but with an area penalty

- High security applications benefit from the extreme difficulty of extracting the programmed data either by visual inspection or power analysis when a differential read mode is used

- A few-time programmable option (eMTP) is straightforward to implement

1T-OTP Examples

Example 1: Replacing External NVM with Embedded 1T-OTP for Media Processor Code Storage

Storing code on-chip using 1T-OTP memory instead of on an external memory chip results in several benefits. Putting code storage on the processor chip instead of implementing it externally saves overall system power and also reduces system Bill of Materials (BoM) cost and area. Overall memory and system security is increased, since you are not transferring code between chips and the embedded 1T-OTP memory is inherently more secure than external EEPROM or flash memory. Since code can be executed-in-place from the 1T-OTP, you eliminate the need for on-chip SRAM to store code transferred from external NVM, thus reducing overall on-chip SRAM requirements. Finally, when used in an eMTP mode the 1T-OTP can be used as a few-time-programmable memory to update stored program or boot code.

Example 2: Using a Multi-purpose 1T-OTP Macro for a Wireless IoT Processor

One of Sidense’s OTP products is the SHF macro family. Sidense SHF memory IP is provided as a complete, non-volatile memory subsystem providing interfaces and features to support a range of embedded SoC applications. The SHF module integrates the OTP memory and Integrated Power Supply (IPS) hard macro blocks along with program control, programming and test interface, error correction and Built-In Self-Test (BIST) RTL.

In this example, the Application Microcontroller core uses an SHF 1T-OTP macro to store boot code (gold blocks). The Wireless LAN Controller and RF circuitry (using the same SHF macro which stores boot code) uses OTP code to implement highly secure storage for encryption keys and secure communications (green blocks). The chip also uses the SHF macro to provide trimming for external environmental sensors, to store configuration settings to adjust and configure analog circuitry during test and assembly and for in-system/in-field adjustments in final equipment (purple blocks)

Author Biography

Jim Lipman is Sidense's marketing director. His work experience includes positions at TechOnLine, VLSI Technology, Hewlett-Packard and Texas Instruments. Jim has a D.Eng from SMU and an MBA from Golden Gate University. He can be reached at jim at sidense dot com.