By Scott Lewis, City Semiconductor, Inc.

Introduction

When continuously running a high speed ADC, it can be a challenge to deal with the firehose of raw data available at the output. To use City Semiconductor’s 2.5 GS/s 12-bit ADC, for example, 30 gigabits per second of data have to be accepted.

The main architectural choice for this problem is whether to process the data on chip or to send it immediately off chip. Both of these options have design implications that need to be considered from the start. In order to get the data off-chip using a reasonable amount of pins, a serializer (SERDES) or LVDS interface must be designed, along with all of the peripheral circuits that it requires. Using the data on chip doesn’t have the limitation for the number of pins, but care must be taken in order to ensure a clean hand-off between clock and supply domains.

On-Chip Data

City Semiconductor’s IP allows the high speed ADC to be placed on the same chip as other functional blocks and circumvent the need for SERDES, allowing significant design cost savings. There are still several problems that need to be solved, but can be approached with conventional circuits that don’t have long design times.

Timing Considerations

One such problem is that in time interleaved designs, there are many groups of data outputs that update sequentially. In order to utilize a single data clock, a multi-stage retiming strategy is needed. The general idea is that the interleaved phase clocks can be reused to latch data from other phases during a time that those data are held stable, ensuring maximum setup and hold time. Data is then presented to the output all at once on a single clock phase.

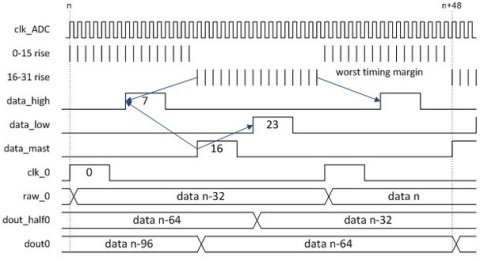

An example of this idea is a 32-way interleaved design. The timing details are shown in figure 1. The clock generator outputs 32 clock phases for each slice that are each separated by 1 high speed clock period. The raw data for each of the slices updates one at a time on the rising edges of these clocks. If a single retiming phase was used, there would be one slice with the hardest timing requirements, and every other slice would be easy. In order to ease the hardest requirements, the data is retimed in groups. Slices 0-15 can be retimed with phase 23, and slices 16-31 can be retimed with phase 7. These two groups can be retimed again with a phase between them so that all the data updates on the same clock. This strategy ensures that the data is not changing for several phases around the retiming clock and special treatment is not required. The main cost for this extra margin is latency.

Figure 1: Timing Details for Data Output

Crossing Supply Domains

Once the retiming strategy is used, there are now many latches all firing at the same time. The data outputs can travel long distances across the chip and have high capacitive loads and need large drivers. As a consequence of this, there will be a big transient current spike on the supply voltage connected to these latches and drivers. Usually a clean analog supply is used throughout the ADC array, but a core digital supply should be used here in order to prevent any fixed frequency IR drop from corrupting the analog signal. Routing the digital supply into the core ADC area should be safe as long as there are no overlapping current paths between the domains.

Crossing Clock Domains

Another timing requirement is that the ADC should be able to present stable data for an external digital block to capture it with its own clock with unknown phase alignment with the ADC or data clock. This problem can be circumvented by using the ADC clock to drive the digital section, but in case this is not possible then extra circuitry needs to be added to ensure a clean handoff. A simple way to achieve this is to build a FIFO. A high word depth is not required as long as it is known that the digital system will take the data as fast as it is generated in normal operation. The main tradeoff for this approach is extra gate count because at least 3 flip-flops and a multiplexer are needed for every bit, but in fine processes this is not a huge area overhead.

Figure 2 shows an example 3-word FIFO with 2 separate clocks for reading and writing. As long as the counters are reset to different values, then the data will never be read at the same time that it is changing. A clock gate circuit (CG) is attached to each FIFO stage so that only one stage is changing at a time.

Figure 2: 3-word FIFO

Off-Chip Data

One way to get the data off chip is to simply translate it to LVDS and send it out in parallel. This method does not require any training patterns or accurate clock phase generation, but may require too many pins depending on the application.

To drive data off-chip at a reasonable speed without using too many pins, a serializer must be used. The SERDES alone adds significant complexity to the design, but even if SERDES IP is already on-hand, it must be connected to the ADC properly.

Figure 3 shows a possible block diagram of the overall ADC IP using a SERDES to drive off chip. In this example, each SERDES lane uses a baud rate based on the ADC clock, so a PLL is not required. The embedded clock generator does still have to generate this clock and meet all timing requirements to ensure internal data fidelity.

Figure 3: Block Diagram of ADC with SERDES Driver

If the ADC clock cannot be used for the SERDES, a clock handoff block needs to be implemented similar to the way it needs to be handled for crossing clock domains on-chip. Even if the ADC clock is used, care must still be taken to ensure the SERDES divider powers up in a known state. One way to do this is to send a synchronization signal based on the clk gen divider that resets the SERDES divider so that the two dividers are always in a relative alignment.

Conclusion

There are many intricacies with using the high speed data stream coming from a gigasample ADC, and some of them were covered here. How a design solves this problem can drive major architecture choices such as utilizing the data on-chip vs. off-chip and should be considered very early on in the definition phase. The main things to consider are circuitry overhead, design difficulty, and latency. A good design will trade off these factors to best fit each unique set of requirements.

About City Semiconductor, Inc.

City Semiconductor is a mixed-signal IC design house providing world-class intellectual property for the highest-speed applications, specializing in data converters (ADC’s and DAC’s) that operate in the Gigahertz range. City Semiconductor also provides custom and semi-custom design and layout services, and turnkey prototyping services. Their quickly-growing portfolio includes proven designs implemented in nodes ranging from 14nm to 180nm, at popular foundries worldwide.

City Semiconductor is located in San Francisco, California, and can be found at www.citysemi.com

Or visit the Design & Reuse partner page