Tom Thomas, Nanda Kumar, Sharath N (SILABTECH Pvt. Ltd)

Abstract:

Mixed signal IP design and verification have become increasingly complex and compute-intensive. It is important to detect any functional or, in worst case, architectural bugs early in the design cycle to avoid late redesigns / costly respins. Modelling and verifying complete behavior of the IP provides both digital and analog designers the required confidence and clarity in design before proceeding into device level designs. In mixed signal designs, RTL and AFE (Analog Front End) designs depend heavily on each other. Validating the correctness of analog-digital interface is also a key concern in such scenario.

In this paper we present a methodology to model and verify a mixed-signal IP using SystemVerilog in Virtuoso and NCsim. We take our 12.5Gbps transmitter (TX) design as an example to explain the method we propose. This TX is designed to operate at programmable data rates from 1.25Gbps – 12.5Gbps and to support requirements of multiple serial protocols like USB, PCIe, and SATA. Interaction between AFE and Digital is key towards proper implementation of features like Feed Forward Equalization (FFE), programmable output swing and power management states. Modelling of the IP such that all probable combination of settings can be exercised and verified with minimum time and resources is a major challenge in situations like this. This paper proposes a new modelling methodology to address these challenges.

1. Introduction

Manually creating models for large IPs is error prone and extremely difficult to debug. We propose a method where only selected key leaf cells in an AFE (Analog Front End) design are modelled and a hierarchical top level model is subsequently generated directly from AFE schematic. This method ensures that AFE model exactly reflects the actual AFE implementation. Section 2 explains this proposed method and its advantages over conventional method. SystemVerilog allows to choose levels of detailing required while modelling an IP. Real number based modelling (RNM) in systemVerilog allows modelling the AFE behavior closer to actual behavior of the circuit. So critical parts of the AFE can be modelled to show the actual analog behavior. Less critical sub-blocks could be modelled at a higher abstract level. Choice of blocks which are modelled is the key to this activity. Section 3 explains choice of abstraction for various sub-blocks and guidelines for subsequent steps to generate top level AFE model. In section 4, application and results of the proposed method in design and verification of a 12.5Gbps TX SERDES IP are presented. Finally in section 5 we have the conclusion.

2. Ideal Mixed Signal Verification Setup

IP verification is an extremely challenging task given the size and complexity of modern day designs. Verification of a Mixed Signal IP adds a whole new set of challenges on top of this. Analog-digital dependency is the most important among those. In many cases there are feedback loops which pass through both analog and digital domains. Digital trim codes for PLL control, trimming of termination resistance of transmitter etc. are a few examples of such inter-domain feedbacks. In such cases verification should not only involve checking correctness of RTL design, but also of the ANA-DIGI interface and of the actual response of AFE to varying digital controls. So, verification is no longer limited to RTL but to the entire IP. An ideal mixed signal verification setup must be able to observe analog responses like PAD voltages, power-up time, supply sequencing requirements, signals crossing multiple power domains etc. and also validate the analog architecture.

Most of the above requirements are met by an AMS simulation. However the time and compute penalty is so huge that it is almost practically impossible to reach the targeted functional / code coverage for any large IP. So, even though SPICE simulations with transistor level netlist is the golden standard for analog IP verification, it cannot be used for fast full-chip simulations. To achieve reasonable simulation speeds, analog behavioral model can be used along with RTL. This enables the complete IP to be simulated in digital solver at near-digital simulation speeds. RNM modelling of AFE in SystemVerilog and then performing a digital-on-top simulation in NCSIM will provide both speed and required accuracy. Efficiency of such a verification setup is highly dependent on the quality of AFE model which goes into simulation along with RTL.

In a typical mixed signal IP design, both RTL & analog schematic are developed in parallel. In conventional IP design flow RTL is usually verified with handwritten analog models in the initial stages. But the hand written analog models itself may not be accurate. So there is no guarantee that implementation of Finite State Machines (FSM which are dependent on ANA-DIGI handoffs is bug free. When analog designers complete AFE design, which happens much later in the design cycle, a few critical use cases are verified using AMS simulation. Since AMS is performed with limited scenarios, it doesn't either give enough confidence for the designers to freeze their designs. And in most cases bugs are caught later, forcing need for complex ECOs or sometimes band aid fixes.

So ideally, AFE models need to be available very early in the design cycle and it has to be detailed enough to capture important details in analog implementation, yet abstract enough to allow fast simulation. Ideally, it should also allow block level importation with full visibility into signals in AFE, thus providing an ability to debug the blocks if errors emerge. Conventional flat handwritten AFE models are never signal-flow models and are hard to maintain or debug. So we propose a method to create a hierarchical model of AFE directly from the AFE schematic, where only a selected few leaf cells need handwritten models. This makes the AFE model not only an exact replica of actual implementation but also with full visibility of internal signals, which makes it easier to maintain and debug. With proper selection of abstraction level for each block, such an AFE model will provide almost all the requirements of an ideal mixed signal verification setup: ability to verify functionality of complete IP with speed, reliable accuracy and with full visibility of internal signals.

3. Guidelines for AFE Model Generation

a. Create “model-able” schematic.

Method proposed in section 2 requires generating AFE model directly from AFE schematic. So while creating the schematic for AFE it has to be kept in mind that the schematic hierarchies are “model-able”. If a sub-block is expected to be netlisted “as is” while generating the final AFE model, then there should not be any PDK elements, like NMOS, PMOS, resistor etc. used at that level. All PDK elements should be placed in cell views for which SystemVerilog model is available. For example, a resistor can be enclosed in a cell view and modelled at the most abstract level as a transmission gate, which simply passes its input to output.

b. Model leaf cells (only).

If AFE schematic hierarchies are created such that they are model-able, as mentioned above, then we can go ahead and model the sub-blocks. Models should ideally be written only for leaf cells. Models for all other blocks should be created using these leaf cell models. This has the advantage of keeping AFE model hierarchical and easier to trace signal flow. For example, to model a serializer it is required to model only its sub-blocks: latch and mux. Model of serialiser can then be generated using models of latch and mux as shown in Fig 1-3 below.

Figure 1: Latch model

Figure 2: Mux model

Figure 3: Serialiser model

c. Choose proper abstraction levels.

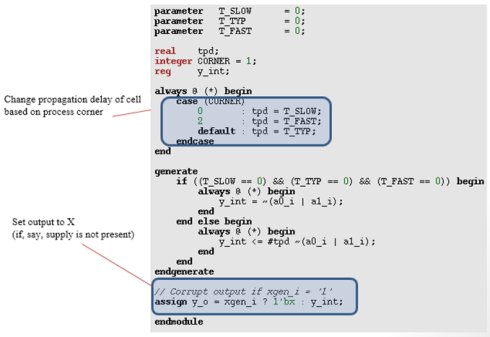

Proper selection of abstraction of each model is key towards increasing the efficiency of verification. Abstraction level should be chosen based on the intended purpose of the model. Functional models can be done at a higher abstraction level than models for performance evaluation. Making functional models which mimic exact analog behavior is usually an overkill in terms of time and compute resources. Functional models (with RNM) is mostly sufficient for doing verification of a mixed signal IP. Use of real number should be limited to modelling “analog” behavior. Use “reg” to model logic data paths. #delay can be used to model power up time of analog circuits. Similarly, as shown in fig 4, parameters can be defined to model process specific characteristics like propagation time, rise / fall time etc. Also, assigning outputs can be made dependent on power supply to create power aware outputs.

Figure 4: Modelling Process and Supply dependence in leaf cell

d. Generate top level model using config view

Top level model for an AFE can be generated from schematic by stitching together models of leaf cells using Virtuoso Hierarchy Editor. In config view select appropriate views (schematic / SystemVerilog) for each cell. Verilog Environment for SystemVerilog integration can be brought up from any schematic editor window through Plugins ïƒ Simulation ïƒ SystemVerilog. Final top level model netlist for AFE can be generated from this environment.

Generating AFE model using this method ensures that the model exactly matches the actual analog implementation. Manually modelling connectivity between various blocks is highly error prone, especially as size and complexity of IPs grow. It is also possible that a functionality is modelled correctly but implemented incorrectly in design. All such bugs are guaranteed to be caught if the AFE model is netlisted from actual AFE schematic. AFE model created by above procedure can be directly handed over for integration and verification with RTL.

4. Verification of 3-TAP FFE for 12.5Gbps Transmitter

In case of our transmitter IP we chose to model only the logic gates and a selected few analog blocks inside the design. Modelling of each of these circuits was done in detail, which made it possible to simulate them for TYP, SLOW and FAST conditions in NCsim. Models for circuits like LDO and bandgap reference accounted for power up times which helped to validate the correctness of power up sequence. Finally the PAD of transmitter was modelled using RNM as shown in fig 5 to provide actual analog voltages and impedance at the output, based on control signals received from RTL. This implies that digital designer can observe the actual analog voltage steps happening at the PAD during FFE transmission.

Figure 5: Real Number Modelling of Transmitter PADs

Fig 6a below shows pre-emphasis, de-emphasis and boost levels at the output of TX model for a specific FFE setting. Fig 6b shows the same outputs from an actual AMS simulation. The level of correspondence between the two plots from Fig 6a and Fig 6b indicates the accuracy of the model. When this model of AFE is taken along with RTL into NCsim for functional verification, a single digital testbench can validate the complete IP design end-to-end much before the actual AFE transistor level netlists are available.

Figure 6: Transmitter Output:

a) From SystemVerilog Model

b) From AMS simulation

RTL consisted of several controls to power up the AFE, trim termination resistance, set 3-tap Feed Forward Equalizer (FFE) filter etc., all of which could be verified only with an accurate AFE. Critical aspects of the design like data path integrity from parallel interface to serial driver and complex control systems like FFE filter implementation was simulated in NCsim. An accurately modelled AFE was vital in ironing out implementation bugs within the RTL as well as analog-digital interface which would have otherwise been caught only during AMS or, in worst case, during silicon characterization.

From a verification perspective, the functionality got verified in early stages of the design cycle without the huge compute and time overhead associated with AMS simulations. This helped in functional and code coverage closure of the design, thereby the quality of the IP was assured. As an example, FFE with over 50K+ configurations was exhaustively verified, which would not have been possible with conventional AMS alone. The AMS plan was thereby minimized to only contain random and corner case configurations, which matched results obtained earlier from the RTL+AFE model simulations. Accurate modelling of AFE also allowed use of automated checkers in digital testbench to check if output of transmitter is compliant to electrical requirements of various protocols.

Shifting of scenarios from AMS to RTL simulation resulted in reduction of time per simulation from 2.5 hours to 3 minutes. To put this number in perspective, even if we were to exercise only a selected set of all valid FFE/Trim settings using transistor level netlist it would have taken ï‚»2 years of simulation time. With the method proposed here, all valid FFE/Trim settings and corresponding AFE responses were validated in less than 5 weeks, thus achieving the required functional and code coverage for the entire IP.

5. Conclusion

In a mixed-signal IP, code coverage closure of RTL is meaningful only when the corresponding AFE response is also verified. A new method was proposed which allows observing actual AFE behavior and at the same time provides fast and reliable functional and code coverage closure of complete IP. This approach also has the benefit of pushing the verification of IP to a very early stage of design cycle. End-to-end validation of a mixed signal IP and exhaustive validation of analog-digital interface can be done much before the actual AFE transistor level netlist is available. Proposed methodology was successfully applied for modelling and verifying a 12.5Gbps SERDES transmitter IP.

References

- Solutions for Mixed-Signal SoC Verification Using Real Number Models Sathishkumar Balasubramanian, Pete Hardee, Cadence Design Systems

- SystemVerilog LRM