Phil Burr and Tim Menasvet, ARM

March 2017

Introduction

The availability of the ARM Cortex-M0 processor within ARM’s DesignStart portal makes designing and prototyping a Cortex-M0 based system-on-chip (SoC) much easier. Quick and free-of-charge access to one of the most licensed Cortex-M processors speeds up the development and validation of new, custom SoCs that will enable the growth of smart connected devices.

Combine this with the availability of a low-cost, simplified, fast-track license to the Cortex-M0 for the commercialization phase of the development means that a custom SoC based backed by the #1 ecosystem of tools, software and operating systems is now more readily available.

So what is this Cortex-M0 DesignStart package and what can a developer do with it?

The first thing to know is that there are two components to the Cortex-M0 DesignStart. The first component is the Cortex-M0 DesignStart Design Kit, which is an RTL package containing the Cortex-M0 DesignStart processor preintegrated with an AHB sub-system. In the hands of a Verilog system designer, the package allows for system design and simulation with a suitable Verilog simulator. The second component is the Cortex-M0 DesignStart FPGA Prototyping Kit, which is an FPGA image of the Cortex-M0 DesignStart processor pre-integrated with an AHB subsystem that works with ARM’s Versatile Express MPS2 FPGA prototyping board. The AHB subsystem portion of the FPGA image can be customized, by adding or removing logic, to the users’ system requirements.

The two components allow a system designer to design and test on a simulator, and then move their design to an FPGA for hardware prototyping.

The Cortex-M0 DesignStart Design Kit can be accessed via the ARM DesignStart portal (designstart.arm.com). Users will need to register, and once approved an email will be sent with instructions on how to download the kit. We do need to do some checks before approving and we do need to set up users on the system, hence it may take approximately one week to do this. For those users who wish to move on to FPGA simulation, instructions on downloading the Cortex-M0 DesignStart FPGA Prototyping Kit are provided in the Design Kit.

By agreeing to an on-line end user license agreement (EULA), the two components can be easily accessed and used for design and prototyping. Once ready for manufacturing, a simplified fast-track license agreement offers the licensee rights to manufacture the Cortex-M0 based device through a low-cost, standardized license agreement. More information on the fast-track purchasing option can also be accessed at designstart.arm.com.

There are some requirements, in terms of tools, that potential users of the Cortex-M0 DesignStart Design Kit and of the Cortex-M0 Design Start FPGA Prototyping Kit, should be aware of. In addition to providing an overview of these two components, this white paper describes these tool-related requirements.

What is the Cortex-M0 DesignStart Design Kit?

The Cortex-M0 DesignStart Design Kit is intended for system Verilog design and simulation of a prototype SoC-based on the Cortex-M0 DesignStart processor.

The DesignStart Design Kit includes:

- The ARM Cortex-M0 DesignStart processor

- An example system-level design for the ARM Cortex-M0 processor

- Reusable AMBA components for system-level development

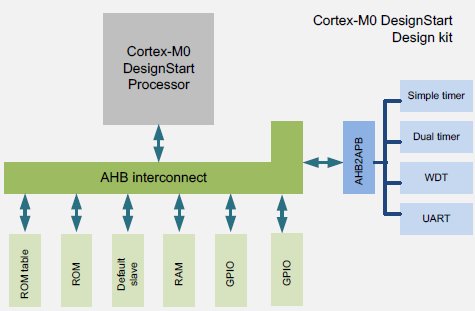

Figure 1: ARM Cortex-M0 DesignStart Design Kit simplified block diagram

The Cortex-M0 processor within DesignStart is delivered as a preconfigured and obfuscated, but synthesizable, Verilog version of the full Cortex-M0 processor. As such, it does not offer the same configurability capability as the full Cortex-M0 processor (which is available within a simplified, low-cost, fast-track licensing option), nor does it offer a hierarchical RTL deliverable for optimal implementations of the SoC. The Cortex-M0 processor within DesignStart does, however, provide a fully compliant ARMv6-M architecture processor that enables system design and simulation. In addition to the Cortex-M0 processor, a pre-integrated AHB subsystem with a useful starter set of peripherals (such as timers, GPIO, UARTs, WDT, etc.) are included to accelerate the users path to a customized functional system.

| Cortex-M0 processor version in DesignStart | Standard Cortex-M0 processor (available with a simplified, lowcost, Fast Track licensing option) | |

| ARMv6-M compatible | Yes | Yes |

| RTL deliverable | Obfuscated, flattened, gate-level Verilog | Documented, unobfuscated Verilog |

| Configuration options | No | Yes |

| Interrupt lines | 32 | 0-32 |

| Multiplier | fast | Slow or fast |

| Debug | No in RTL (as it is not used in RTL simulation) Yes in FPGA | Yes (optional) |

| Low power mode support and WIC | No | Yes |

Table 1: Comparison between Cortex-M0 DesignStart processor and the full Cortex-M0 processor

Benefits of the full Cortex-M0 processor

The Cortex-M0 processor within DesignStart is not intended for a production system on chip. It is intended for system Verilog design and prototyping. As such, the full Cortex-M0 processor provides additional capabilities above that of the Cortex-M0 DesignStart processor. These are:

Low power optimizations

The full Cortex-M0 processor is designed for deployment in a multi-power domain system to maximize static power efficiency, featuring a minimal Wake-up Interrupt Controller (WIC). It also makes extensive use of architectural clock gating to minimize dynamic power. For simplicity these are amongst the technologies not included in the Cortex-M0 DesignStart processor.

Debug support

The full Cortex-M0 processor supports the use of an external hardware debugger to facilitate the development of applications. Connection is possible via either Serial-Wire or JTAG interfaces and provides a host of debug functionality. Both connections provide the ability to access all AHB-Lite connected slaves, including RAM, whilst the processor is running, as well as providing full halting-mode debug. Halting-mode debug allows all processor registers to be examined and modified, and can be configured to provide up to four hardware breakpoints and two hardware watchpoints. Unlimited software breakpoints are possible via the BKPT instruction.

Full debug supported is included within the Cortex-M0 DesignStart FPGA Prototyping Kit package so that designs can be debugged on FPGA. Debug is not included within the Cortex-M0 DesignStart Design Kit RTL as this unit is not required in RTL simulation. Note: to facilitate the ease of transition from the RTL simulation to the FPGA prototyping phases, debug pinout from the processor is included in the RTL package.

Hardware multiplier options

The ARMv6-M architecture provides a MULS instruction capable of performing a 32-bitx32-bit multiply, generating a 32-bit result. The full Cortex-M0 processor product allows implementation time selection between a fast single-cycle implementation and a low-area 32-cycle implementation. The Cortex-M0 processor within DesignStart only provides the single-cycle option.

Jitter-free interrupt handling

The full Cortex-M0 processor provides the capability to optionally regulate the time between an interrupt-signal being asserted and the point at which the associated exception handler is entered, thus providing zero-jitter interrupt entry. The Cortex-M0 processor in DesignStart always handles interrupts as fast as possible.

Requirements for using Cortex-M0 DesignStart Design Kit

The Cortex-M0 DesignStart Design Kit can be used for system design and simulation. Appropriate ASIC system design tools are required for each of the steps in the development flow. The Cortex-M0 DesignStart Design Kit has been validated with the following tools:

| Tool | Version |

| Verilog simulator | Cadence Incisive 10.20.010 Mentor Questasim 10.3b Synopsys VCS 2011.12 |

| C Compiler | RVCT 5.06.21 |

| Synthesis | Synopsys Design Compiler 2013.03-SP5 |

| Formal equivalence check | Synopsys Formality 2013.03-SP5 |

Table 2: Example of tools used for validating Cortex-M0 DeisgnStart Design Kit

Design Services

EDA tooling

To help get started with a Cortex-M0 design, ARM has partnered with both Cadence Design Systems and Mentor Graphics to provide simplified and expedited access to chip development tooling, and a free evaluation of the Cortex- M0 within these tools. Instructions on accessing this EDA tooling will be sent to approved registrants of Cortex-M0 DesignStart.

Design services companies

Companies wishing to supplement their own skills can use ARM Approved Design Partners who are experienced in developing SoCs using ARM IP. ARM Approved partners have been through a robust audit process before they are recommend. The process includes: track record of success, audited quality and management procedures, highly qualified engineering teams, financial stability and business continuity planning.

ARM Approved design partners include: eInfochips, Open-Silicon, SoC Solutions, and Sondrel

What is the Cortex-M0 DesignStart FPGA Prototyping Kit?

The Cortex-M0 DesignStart FPGA Prototyping Kit is an encrypted FPGA image of the Cortex-M0 processor together with a customizable example AHB subsystem. The Cortex-M0 is configured exactly the same as the obfuscated RTL version. The prototyping kit is only usable on the ARM MPS2 board as the encrypted FPGA image is only decrypted by a key pre-installed on the MPS2 board.

Requirements for using Cortex-M0 DesignStart FPGA Prototyping Kit

Usage of the Cortex-M0 DesignStart FPGA Prototyping Kit requires the purchase of the ARM Versatile Express MPS2 board. More information on this board can be found here: https://www.keil.com/boards2/arm/v2m_mps2/

Unlike the Cortex-M0 processor in the DesignStart Design Kit, the encrypted image of the Cortex-M0 DesignStart processor contains debug logic that supports SW development and debug on the ARM MPS2 board. The AHB subsystem delivered with the FPGA prototyping kit is modifiable, allowing the user to customize logic surrounding the DesignStart processor. This customization process relies on technology supplied by Intel’s Quartus FPGA design tool called partial reconfiguration. Usage of the partial reconfiguration feature requires that the Cortex-M0 DesignStart FPGA project must use the latest Intel Quartus Prime subscription edition (version 15.0 at the time of this writing). Quartus Prime Lite is not suitable. More information on the Quartus Prime subscription edition tool can be found here: https://www.altera.com/products/design-software/fpga-design/quartus-ii/quartus-ii-subscription-edition.html

In order to enable the partial reconfiguration feature, an additional (free of charge) license is required to the basic Quartus Prime subscription edition license. If you do not have the partial reconfiguration feature enabled in your existing license please contact mps-support@arm.com to request a partial reconfiguration license.

Summary

The Cortex-M0 DesignStart Design Kit provides a Cortex-M0 and a system design kit provides free access to IP to enable designers to design, simulate and test Cortex-M0 based systems. With this kit, designers can add their own or third party IP to the system, and get a long way with their SoC design with minimal risk. The Cortex-M0 DesignStart FPGA Prototyping Kit enables designers to then test their design on an ARM-supplied FPGA platform.

Once ready to commercialize, designers then have a simplified route to license the full IP, with a low-cost, fast-track licensing option.

Learn more about DesignStart - fast, free access to industry-leading ARM IP for evaluation, with a fast-track licence for commercialization.

Stay up to date with the latest resources, updates and discussion about custom SoC design with ARM IP – join the ARM DesignStart Community for free.