Bonny Vora, eInfochips

Abstract

Increasing size and complexity of designs and systems have made it mandatory to randomize the stimulus driven to these designs, as directed scenarios will take more time to complete the verification. Along with randomization, there is a need of same design code to be exercised multiple times, this is achieved through multiple simulations of same test sequence. The test sequence will include the feature specific randomization. During multiple runs of test sequence, the randomization will provide different stimulus for design. To increase the quality and reach of the verification, these test sequences need to be combined to form a new test. When multiple test sequences are combined, there could be a need to randomize the order in which these sequences are simulated. UVM has made this requirement easy for verification engineers by introducing uvm_sequence_library. Verification engineer need to derive a project specific uvm_sequence_library and register the test sequences with this library class. Once the sequence library is started from the testcase, the registered sequences are randomly selected and executed. The default randomness in selecting the sequences enables the verification team to find corner scenarios in faster manner. The sequence library concept can allow verification engineer to configure the regression specific sequence library as well. The paper introduces the sequence library concept by explaining the usage, advantages and limitations.

Keywords:

UVM, Sequence Library, Randomization, Regression

1- Introduction

The stimulus generation requires randomization of transaction class variables. The randomization of transaction class variables is controlled in test sequences, which are derived from uvm_sequence. The “body” method of the uvm_sequence is over written to define the test specific randomization of transaction class variables. Such multiple derived test sequences can me merged in single test sequence to further increase the random nature of stimulus. Such merging can be achieved by using uvm_sequence_library. The uvm_sequence_library provides a means to register multiple test sequences. Upon starting the uvm_sequence_library from a test, all the registered sequences are executed randomly by default for random number of times. The uvm_sequence_library also provides control to user in terms of sequence selection logic and which sequences to execute.

As the name suggests, uvm_sequence_library is the library of multiple sequences extended from uvm_sequence. As shown in above figure 1, uvm_sequence_library is extended from uvm_sequence, just like other user-defined sequences. Apart from uvm_sequence advantages, it has its own control logic to run the sequences. Once started, sequence library randomly selects and executes a sequence, depending on the selection_mode set by user.

Figure 1: Sequence library hierarchy

uvm_sequence_library = uvm_sequence + Controls to run sequence

1.1 SEQUENCE REGISTERATION INSIDE SEQUENCE LIBRARY

UVM provides means to register single sequence as well as list of sequences. Each of these are explained with code snippet below.

1. Calling “add_typewide_sequence” from sequence library

class my_seq_lib extends uvm_sequence_library #(my_packet);

. . .

function new(string name = "my_seq_lib");

. . .

add_typewide_sequence(my_seq::get_type());

add_typewide_sequence(my_seq2::get_type());

endfunction

. . .

endclass: my_seq_lib

2. Calling “add_sequence” from testcase

class my_test extends uvm_test;

. . .

virtual function void build_phase(uvm_phase phase);

. . .

seq_lib.add_sequence(my_seq::get_type());

seq_lib.add_sequence(my_seq2::get_type());

endfunction: build_phase

. . .

endclass

3. Calling “`uvm_add_to_seq_lib” from testcase

class my_test extends uvm_test;

`uvm_add_to_seq_lib(my_seq, my_seq_lib)

`uvm_add_to_seq_lib(my_seq2, my_seq_lib)

. . .

endclass

4. Calling “add_typewide_sequences” from sequence library

class my_seq_lib extends uvm_sequence_library #(my_packet);

. . .

function new(string name = "my_seq_lib");

. . .

add_typewide_sequences({my_seq::get_type(),

my_seq2::get_type()});

endfunction

. . .

endclass: my_seq_lib

5. Calling “add_sequences’ from testcase

class my_test extends uvm_test;

. . .

virtual function void build_phase(uvm_phase phase);

. . .

seq_lib.add_sequences({my_seq::get_type(),

my_seq2::get_type()});

endfunction: build_phase

. . .

endclass

1.2 SEQUENCE LIBRARY CONTROLS

Sequence library behavior can be controlled by below properties:

- min_random_count: Minimum constraints for how many sequences to run

- max_random_count: Maximum constraints for how many sequences to run

- selection_mode: Sequence selection algorithm

- UVM_SEQ_LIB_RAND: Selects the sequence randomly

- UVM_SEQ_LIB_RANDC: Selects the sequence in random cyclic order

- UVM_SEQ_LIB_ITEM: Generates sequence item only, sequence won’t be executed

- UVM_SEQ_LIB_USER: Selects the sequence based on the algorithm defined by user inside function “select_sequence”

Example of accessing sequence library controls,

class my_test extends uvm_test;

. . .

virtual function void build_phase(uvm_phase phase);

. . .

// Minimum and Maximum Sequence iteration count

seq_lib.min_random_count = 5;

seq_lib.max_random_count = 10;

// Sequence selection mode

seq_lib.selection_mode = UVM_SEQ_LIB_USER;

endfunction: build_phase

. . .

endclass

In UVM_SEQ_LIB_USER mode, example code of overwriting “select_sequence” in sequence library, (Below code will only execute “my_seq” and “my_seq2”)

function int unsigned select_sequence(int unsigned max);

int current_seq;

do

begin

void'(std::randomize(current_seq) with {current_seq inside {[0 : max]};});

end while (sequences[current_seq] != my_seq2::get_type()

&& sequences[current_seq] != my_seq::get_type());

return current_seq;

endfunction: select_sequence

1.3 Caution : <pre_body> , <post_body>

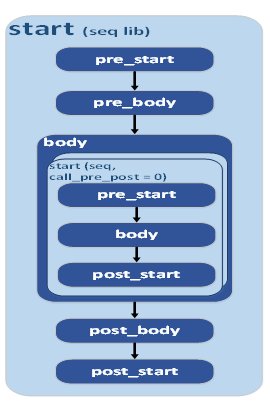

To run sequence library, just like other sequences, user has to call the <start> method of sequence library. This <start> method calls the <body> method of sequence library. Here based on the sequence selection mode, sequence library selects the sequence and executes its <start> method.

As per UVM [Ref: uvm_sequence_base.svh (Line number: 65)], “A sequence can also be indirectly started as a child in the body of a parent sequence by invoking `uvm_do macro. In this case <start> is called with ~call_pre_post~ set to 0, preventing the standard sequence’s <pre_body> and <post_body> methods are being called.”

Here, when sequence library executes <start> method of registered sequences by calling `uvm_rand_send macro, it passes the call_pre_post argument as 0 which means <pre_body> and <post_body> method of sequence won’t be executed.

Following figure is for reference to visualize the start method flow.

Figure 2. Sequence execution flow

1.4 SUMMARY

Sequence library provides one more pre-defined UVM approach which can be utilized to ease the implementation of creating a test sequence by combining multiple sequences. The sequence library also provides the means to control the sequence selection and number of execution iterations.

Advantages

- uvm_sequence_library is a simple approach where user has to register the sequence and run it. Different combination of sequence execution order may find some of the corner cases in design.

- Single run of sequence library can help to hit more coverage bins and this way user can reduce the simulation time to achieve the targeted coverage numbers.

- Sequence library gives control to user for number of sequences to run and sequence selection mode, which makes it more flexible.

Limitations

- When the user wants to run single sequence to hit any dedicated scenario, this approach is not very efficient, as user has to write extra lines of code for this.

- Sequence reusability won’t be much if user is concerned with <pre_body> and <post_body> method of sequence. As sequence library being a parent sequence doesn’t call the <pre_body> and <post_body> methods of child sequence.

- Usually to run various sequences in different order and for multiple times user writes either script or create one more sequence on top of multiple sequences. This extra overhead can be eliminated by using sequence library approach.

1.5 REFERENCES

- SystemVerilog 3.1a Language Reference Manual, 13th May 2004

- Universal Verification Methodology(UVM) 1.2 User’s Guide, 8th October 2015