Industry Articles

Arteris System IP Meets Arm Processor IP-October 12, 2022 |

By Frank Schirrmeister, ArterisIP

The design of system-on-chip (SoC) devices for automotive applications—and the reuse of portions of those designs for future SoC incarnations—just got a lot easier with the recent announcement of the expanded partnership between Arm and Arteris.

Welcome to the Age of Software-Defined Vehicles

Software-defined vehicles (SDVs) will have features and functions primarily enabled through software with updates and new services delivered over-the-air (OTA). SDVs offer significant safety and convenience features and enable new in-vehicle experiences and functions.

The current trend toward electric vehicles (EVs) is accompanied by the increasing sophistication of advanced driver-assistance systems (ADAS) and ever greater levels of autonomy. Another trend is the “digital cockpit,” which—broadly speaking—refers to the digital experience of the driver and any passengers within the car. This experience is enabled by instrument clusters, multi-screen displays, heads-up displays, advanced navigation systems, infotainment systems and voice assistants, to name but a few.

At the Intersection of Hardware and Software

Of course, software cannot exist in isolation—it needs some form of hardware processing platform to run on.

Early automotive compute architectures featured multiple microcontroller units (MCUs), each focused on a particular task. Recently zonal controller architectures are emerging, often requiring SoCs containing multiple homogeneous processing cores.

The advent of ADAS powered by multi-sensor (vision, radar, lidar, etc.) object detection and recognition systems demands more and more sophisticated combinations of heterogeneous processing capabilities. This is also true of the systems forming the digital cockpit.

All of these requirements explain why today’s and tomorrow’s automotive SoCs feature multiple heterogeneous processing cores and accelerators. These processing cores include central processing units (CPUs), graphics processing units (GPUs) and image signal processors (ISPs). The current generation of such SoCs also often feature one or more neural processing unit (NPU) cores that can perform artificial intelligence (AI) and machine learning (ML) functions much faster than traditional cores while using a fraction of the power.

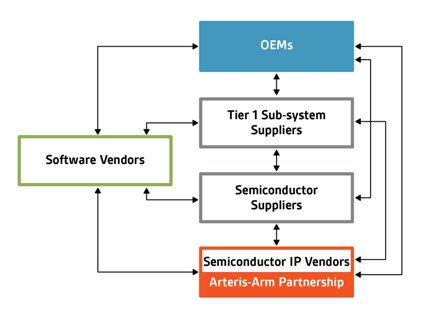

Figure 1. Arm and Arteris sit at the intersection between hardware and software.

No one will be surprised to hear that Arm processor core IP provides a key enabler of automotive technology. In fact, more than 90 percent of in-vehicle infotainment (IVI) systems are powered by Arm-based chips, as are many “under-the-hood” applications, including meter cluster, HVAC control and side- or rear-view mirrors. However, even members of the automotive design community may be surprised to hear that Arteris system IP is used in over 70 percent of today’s ADAS SoCs.

It Is All About the Interconnect

Even the most powerful processing cores are of limited use if quick and efficient communication with each other and system resources is lacking. This is where Arteris system IP enters the picture. For example, Arteris FlexNoC® interconnect IP is used by the world’s top automotive semiconductor design teams as the backbone for their on-chip communications.

It does not matter whether the designers wish to employ AMBA AXI3, AXI4, AHB, APB, OCP, PIF or a proprietary protocol. FlexNoC IP reduces the number of wires by nearly one-half, resulting in fewer gates and a more compact chip floor plan.

Another consideration is that each of the processor cores will contain a local store of data and instructions called a cache. In many cases, multiple cores will share one or more levels of cache. The term “cache coherence” refers to the process of ensuring that a coherent view of the data values is maintained in the multiple caches. Maintaining cache coherence is non-trivial, even in a homogeneous architecture where all of the processor cores are identical. The problems are exacerbated in the case of heterogeneous architectures because processing elements may differ in their coherent interface protocols, cache state models, cache line sizes, caching structure sizing and associativity, transaction race conditions and other features.

This explains why the world’s leading automotive semiconductor design teams employ Arteris Ncore® Cache Coherent interconnect IP, which is optimized for heterogeneous cache coherent systems. In fact, Ncore is the industry’s only multi-protocol AMBA CHI and ACE cache coherent interconnect. Furthermore, Ncore is more scalable and area-efficient than mesh-based interconnects.

Managing Design, Change and Reuse

An SoC design is typically represented as a hierarchical netlist of blocks, with IP blocks themselves as leave components. Many of the IP blocks will come from third-party vendors, while others will be created in-house by the design team. The tasks of creating and managing the design netlist used to be performed by hand, often using an extensible and customizable text editor like VI or GNU Emacs. Today, however, a single IP block may involve a thousand connections and span hundreds of lines of code. This means it is becoming increasingly untenable to directly manage the design by hand.

The best way to facilitate assembly, refinement and update through abstraction and automation is by means of the XML-based IP-XACT standard. Although several companies have developed internal tools that employ IP-XACT, the de-facto industry standard is Arteris IP Deployment Technology.

If an IP block does not already have an associated IP-XACT model, Arteris technology can be used to parse the IP and generate a corresponding IP-XACT model. Similarly, if a hierarchical netlist of the design already exists, the tool can parse this netlist and generate a hierarchical graphical representation of the design. Alternatively, Arteris can display the collection of available IP blocks, and designers can use a GUI to drag-and-drop and connect these blocks and then generate the design netlist.

The real power comes with the fact that it is possible to create scripts in Python, Tcl or Java and to associate these scripts with individual blocks of IP with hierarchical blocks and with the design as a whole. Arteris Magillem application programming interface (API) allows these scripts to be used to perform tasks like the “search-and-replace” of existing IP blocks with later versions of those blocks while also performing appropriate checks, such as ensuring that the ports still match.

The end result is that incorporating Arteris technology into an automotive SoC development environment greatly facilitates the team’s ability to manage design, change and reuse.

Expanding the Arm-Arteris Partnership

Arm and Arteris have been collaborating for many years. As far back as 2011, for example, Arteris announced support for the deployment of Arm’s AMBA® 4 ACE™ specification. More recently, in 2018, the companies gave joint presentations on Implementing ISO 26262 Compliant AI Systems with Arm and Arteris IP. This combined effort described how AI and ML acceleration IP from Arm could be implemented in ISO 26262-compliant automotive systems with the help of functional safety mechanisms in the Arteris FlexNoC and Ncore interconnects.

Figure 2. The expanded Arm-Arteris partnership means Arteris now further strengthens its role in the evolving value chain.

The newly extended Arm-Arteris partnership will facilitate the creation of best-in-class automotive solutions using Arm AE processors and Arteris’ interconnect IP. This means it will be even easier for automotive SoC design teams to take full advantage of Arm processor IP and Arteris system IP (the use of Arteris IP Deployment Technology to manage design, change and reuse is an add-on option should designers wish to take advantage of it).

As part of this collaboration, Arm has licensed a portfolio of released and future Arm Cortex CPUs to Arteris to expand and accelerate the delivery of solutions that will provide the most advanced safety and security capabilities to the automotive market.

This new partnership means the two companies can fully align their roadmaps to deliver seamless integration that results in optimized flows for the best quality of results (QoR) and safety, all of which is key to delivering customer success.

Entering this partnership is a critical intermediate milestone, formalizing the previous interactions and now enabling proactive co-development. Stay tuned for its deliveries over the months and years to come.

Frank Schirrmeister is vice president of solutions and business development at Arteris. He leads activities in the automotive, data center, 5G/6G communications, mobile, aerospace and data center industry verticals and the technology horizontals artificial intelligence, machine learning and safety. Before Arteris, Frank held various senior leadership positions at Cadence Design Systems, Synopsys and Imperas, focusing on product marketing and management, solutions, strategic ecosystem partner initiatives and customer engagement.