By Andy Nightingale, Arteris IP

Today’s system-on-chip (SoC) designs continue to grow in capacity and complexity. The only way to continue developing components of this class is by increasing the sophistication of the design, implementation and verification tools while simultaneously increasing levels of automation. The launch of the latest generation of network-on-chip (NoC) IP, FlexNoC 5, from Arteris addresses all these issues.

More and More Transistors

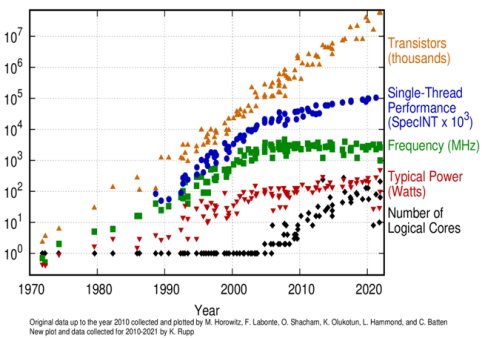

The first commercial microprocessor, the Intel 4004, was made available in 1971. You may recall the various 50th-anniversary articles from a couple of years ago. As part of this milestone, most of us have seen representations of different aspects of microprocessor trend data, epitomized in Figure 1.

Figure 1. 50 years of microprocessor trend data

Observe that the vertical axis is plotted using a logarithmic scale. For example, many aspects of this chart—power, frequency and single-thread performance—start to trail off over time. However, the one feature that continues to grow exponentially is the number of transistors.

These trends are also applicable to system-on-chip (SoC) devices. Even “average” SoCs today can contain hundreds of millions of transistors, while high-end devices may contain billions.

Traditionally, the solution to creating more complex designs has been to “divide and conquer” by adding more engineers and partitioning the project into smaller portions. However, it’s becoming more and more challenging to find skilled architects at this level. Also, treating the design as a single entity throughout the development cycle is becoming increasingly necessary.

The answer is to provide the development team with more sophisticated design tools and increased levels of automation. One such solution is the recently announced next-generation physically aware NoC interconnect IP, FlexNoC 5, from Arteris.

FlexNoC 5 Spans the Development Process

The only way in which design teams can create today’s high-end SoCs is to implement standard functions such as processors (e.g., Arm), communications (e.g., Ethernet, USB and PCI), accelerators (e.g., codecs and cryptographic functions) and so forth using off-the-shelf IP blocks from third-party vendors. This leaves the team free to focus on the IP blocks that differentiate their SoC from their competitors.

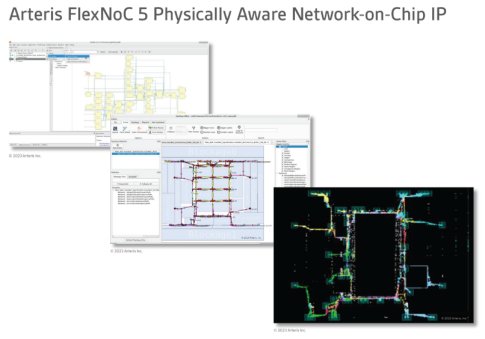

Most IP blocks are square or rectangular and occupy a locally constrained silicon die area. By comparison, NoC IP spans the entire device, which makes it necessary for the NoC design environment to span the development process as a whole, as Figure 2 illustrates.

Figure 2. FlexNoC 5 physically aware network-on-chip IP spans the development process.

(Source: Arteris, Inc.)

At the start of the design cycle, engineers can transfer data back and forth between the FlexNoC 5 and IP-XACT-based Magillem IP deployment technology from Arteris. FlexNoC 5 can import first-pass IP placement data provided by the physical design team’s placement and routing (P&R) tools as the design progresses. Initial placement of NoC IP-related functions—such as network interface units (NIUs), buffers, switches and pipeline stages—can be performed inside the FlexNoC 5 environment. This is particularly important concerning inserting pipeline stages. Too few pipeline blocks will make it hard or impossible to close timing; too many will consume unnecessary amounts of area and power and increase latency.

Iterating between the front-end logical design and the back-end physical design is a time and resource-intensive process. As a result, if front-end designers are obliged to insert pipeline stages by hand, they tend to “over-engineer” the problem by adding too many stages in the hope of minimizing iterations.

FlexNoC 5 interconnect IP tools can automatically insert the pipeline stages and analyze the design to ensure performance goals and timing constraints are met. In addition to generating the RTL associated with the NoC, FlexNoC 5 also creates associated first-pass placement data for all the NoC-related structures. This placement data can be passed to the downstream P&R tools. In addition to significantly lessening the effort the back-end physical placement tools must expend, this also dramatically decreases the number of back-end to front-end design iterations, thereby increasing productivity and reducing time to market.

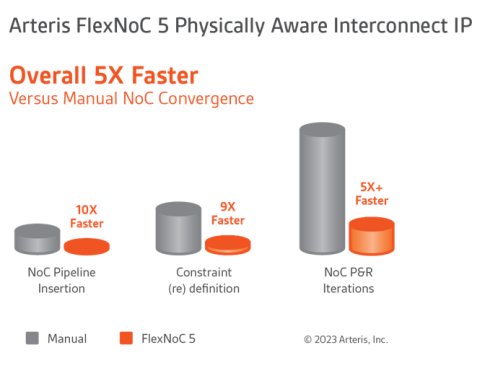

The Proof of the Pudding

There’s an old saying that “the proof of the pudding is in the eating,” which means that the actual value of something can be judged only from practical experience or results and not from appearance or theory. Early users report that FlexNoC 5’s automatic physically aware pipeline insertion is 10X faster than engineers performing this task by hand. Associated constraint definition and redefinition are 9X faster, and the number of place-and-route iterations are dramatically reduced, resulting in an overall 5X speed increase in this massively time-consuming process, as shown in Figure 3.

Figure 3. Productivity enhancements offered by FlexNoC 5 physically aware network-on-chip IP.

(Source: Arteris, Inc.)

As a real-world “proof of the pudding” example, one company reported that they spent 226 days performing these tasks. When the engineers used an early release version of FlexNoC 5 on an equivalent project, the time was reduced to only 22.5 days, providing a 90% timesaving.

Conclusion

To date, interconnect IP and system IP from Arteris have been employed in over 600 SoC design starts. As a result, 3+ billion SoCs leveraging this IP have shipped in electronic systems worldwide. As its reputation for silicon-proven IP has spread, Arteris has gained 65+ new customers in the past two years and is now used in 70% of automotive advanced driver-assistance system (ADAS) SoCs. But it’s not just the automotive market that is taking advantage of a commercial NoC; others, including communications, consumer electronics, enterprise computing and industrial, are looking for silicon-proven system IP solutions to reduce time to market, optimize engineering resources and improve SoC economics.

With the introduction of FlexNoC 5, the fifth generation of FlexNoC technology, Arteris is destined to play a vital role in developing many more state-of-the-art SoC designs in the years to come.