By M31 Technology

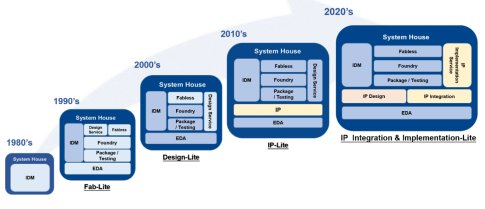

The development of the semiconductor industry can be traced back to the 1980s. At that time, the semiconductor/chip design model was dominated by IDM, which independently completed the entire process from design, manufacturing, packaging, and further market sales of finished chips. However, with the advancement of semiconductor processes and the specialization of manufacturing, the capital investment for production equipment became increasingly enormous, as well as the professional technical expertise were raised. While the large companies could still afford the significant capital expenditures, but for small companies, in order to survive the market competition and compete with large companies on cost, must seek opportunities for outsourcing manufacturing; thereby, an ecosystem of wafer outsourcing and packaging was developed.

The technological evolution of the 2010s led to the trend of more diversified range of features in electronic end products, as well as trends toward portability and smaller size. This increased the complexity of IC chip design and manufacturing, resulting in many design technology issues. For example, AIoT chip manufacturers focusing on core learning and computing functions wanted to include other high-speed interface functions such as MIPI/USB/PCIe for data receiving and transmission, and this required the development of more talents with expertise in high-speed interface design, which significantly increased the operating costs of companies; thus, leading to the development of IP design companies in the market.

Throughout the development of the industry, the evolution of advanced semiconductor manufacturing processes has led to an increase in production costs, high-speed interface bandwidth, and the difficulty and risk in IP and SoC integration. That results in a significant increase in development costs for chip manufacturers, especially in the investment of manpower, and EDA tools are becoming more challenging. Therefore, the demand for IP integration hardening has been increasing, which allows IP companies with expertise in high-speed interfaces and advanced processes to significantly shorten development design cycles, reduce manpower and tool costs, but also improve the probability of successful mass production. To meet this demand, M31 Technology, a global professional IP provider, has further launched IP Integration Service to help customers effectively accelerate time-to-market and gain a competitive edge in the market for their IC products.

SoC Integration Implementation Method -Flatten or Hierarchy Process

With the application of AIoT chips, the demand for both power and performance SoC applications has increased in complexity, as well as the process has evolved to FinFET. The implementation of the chip requires significant costs in terms of timing, manpower, machinery, and EDA software, thus leading to a hierarchy process for highly integrated SoC chips.

For example, the components in an AIoT integrated SoC will roughly include:

- Big Cluster Multi-core CPU: Multi-core system high-speed computing processing unit

- Litter Cluster CPU: standby mode, low-power system processing unit

- GPU: Graphics Processing Unit

- NPU: Neural-network Processing Unit

- Peripheral Device: Peripheral high-speed data access interface, such as USB/MIPI/PCIe/DDR...

- DVFS/Multi-power Domain: Dynamic voltage frequency scaling, multi-power domain

Highly integrated IP is both complex and diverse, in order to save the company's investment resources and effectively control product risks, it is an inevitable trend to move towards the integration of IP segmentation and hierarchical implementation integration.

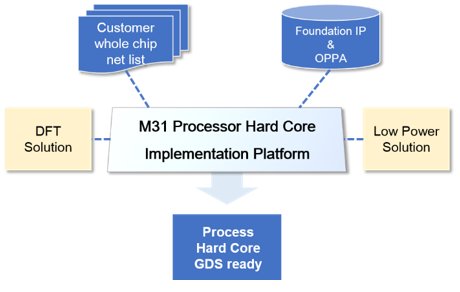

IP Hardcore and Integration

Due to the increased complexity, performance, and power requirements of SoC applications, IP hardcore implementation accelerates the completion of system application specifications. The M31 comes with a series of M31 optimized design kits based on Arm® architecture processors - OPPA (Optimized PPA) library, which includes customized high-speed and ultra-low leakage memory instances and optimized cell library to help customers' chip design teams to achieve their processor and SoC design goals in the shortest possible time (Figure 1, Figure 2).

Figure 1: M31 Processor Hard Core Implementation Platform

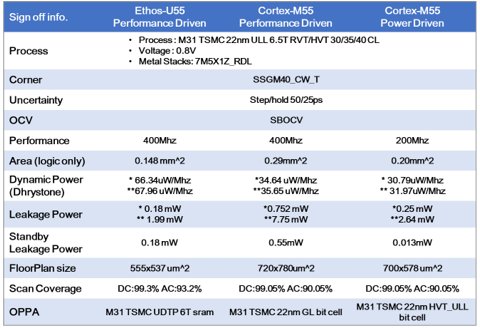

Figure 2: M31 Processor Hardcore Table

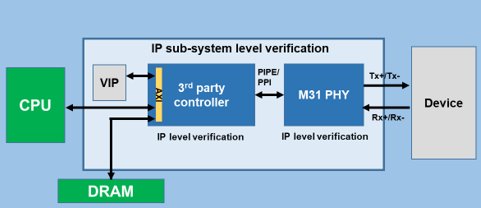

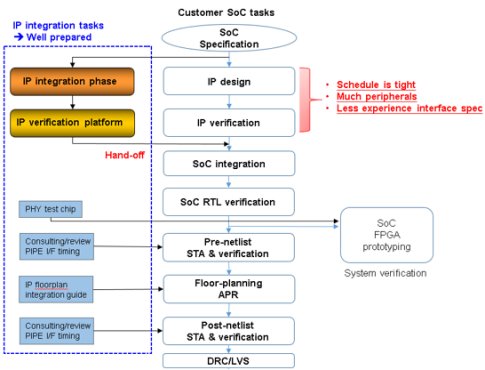

In terms of IP integration, since many high-speed access interfaces in SoCs include PHYs and Controllers, it is important for customers to reduce the high risk of verification, integration, and implementation when they are not familiar with the specialized field of high-speed interfaces. M31 cooperates with professional controller component partners to create an integrated service for the PHY and controller. This includes providing a complete verification process from the IP-level to the high-speed interface sub-system, even to the FPGA platform (Figure 3), and providing consultation services for integration, layout, and timing analysis at different stages of SoC development and implementation (Figure 4). This allows customers to complete high-speed interface silicon IP verification, integration, and implementation with low risk while developing their products.

Figure 3: Sub-system level verification

Figure 4: IP Integration Service

M31 IP Integration Service

Under the rapid evolution of advanced processes, from traditional IDM companies dominating chip development to diversified application fields of SoC, and to professional IP specialization, the process and risk management of chip design are all being tested. As a global professional IP provider, M31 not only provides high quality silicon certified products, but also provides highly integrated hard-core implementation service solutions necessary for SoC chips in the application market that pursues both performance and power efficiency, helping chip design teams to achieve their processor and SoC design goals in the shortest time frame and lowest risk.