Industry Articles

Creating SoC Designs Better and Faster With Integration Automation-June 28, 2024 |

By Insaf Meliane, Arteris

A modern high-end system-on-chip (SoC) design can be extremely large and enormously complex, employing thousands of intellectual property (IP) blocks. Most of these IPs will be sourced from trusted third-party vendors. These will typically be augmented by one or more internally-developed IPs to provide the secret sauce that will distinguish this SoC from its competitors.

The IPs comprising past SoCs were often integrated and configured by hand. However, developing one of today’s SoCs would be impossible without the aid of sophisticated, high-capacity and high-performance integration automation.

Managing Metadata

The term metadata means data about data. In the case of the IPs being used to build an SoC, the metadata view of each IP provides useful information to augment the core functionality of that IP. For example, an IP may have many ports that allow it to communicate with other IPs via a network-on-chip (NoC). The metadata associated with the IP will describe things such as port widths and types, operating frequencies, configuration parameters, communication protocols and other specifications.

In addition to an IP’s core logic, it will also include configuration and status registers (CSRs). These registers allow the IP to be configured and its operation monitored by processor IPs on the SoC and by an external host computer, if required. Each IP may contain hundreds of thousands of CSRs, while the entire SoC may encompass multiple millions of these elements.

CSRs are instrumental with respect to the SoC’s hardware/software interface (HSI), which are the points of interaction between the software—both low-level firmware and higher-level application software—and the underlying hardware. This integration allows for dynamic control and status updates that are vital for the SoC’s functionality and efficiency.

Managing all this metadata can be a logistical nightmare. In the early days of SoC design, much of the metadata was stored in spreadsheets that were created, manipulated and maintained by hand. This is simply not possible in today’s SoC designs, especially in the case of CSRs, which can easily be modified hundreds of times a day in the early stages of the device’s development. For example, CSR bits may be added, removed or renamed, and their hardware/software behavior may be revised.

Many companies and organizations have contributed to standards that have been adopted across the industry. One such standard is IP-XACT, also known as IEEE 1685, which is an Extensible Markup Language (XML) format designed from the ground up to facilitate the management and integration of SoC IPs.

A somewhat related standard is SystemRDL, an open-source, text-based descriptive language that focuses exclusively on registers. Because of some limitations, the original SystemRDL 1.0 has been upgraded to SystemRDL 2.0 to include support for verification-based properties such as constraints, coverage and HDL paths.

CSRCompiler

It’s important to understand the role of standards like IP-XACT and SystemRDL 2.0. They provide the specifications for how metadata associated with IPs should be represented and stored in a machine-readable form that can be generated and consumed by machines. That is, these standards are not tools in their own right. To take full advantage of IP-XACT and SystemRDL 2.0, it’s necessary to have appropriate tools and an associated development environment and methodology.

Some companies may choose to develop their own homegrown tools and infrastructure. These are often realized as a hodge-podge of scripts created using languages like Tcl, Perl and Python. The problem with such in-house developments is that their contributors tend to move on, leaving hundreds of thousands of lines of code that no one knows how to maintain. (There’s an old programming joke about a code comment that reads, “When I wrote this function, only the universe and myself knew how it worked… now only the universe knows!”) Besides, writing and maintaining these homegrown scripts and solutions requires significant manual efforts to generate accurate designs. What used to be doable by hand or with a couple of scripts no longer works with the level of complexity SoCs have reached.

To address these issues, Arteris provides a suite of tools to facilitate SoC creation and management. One of these tools is CSRCompiler, a complete register design solution for hardware, software, verification and documentation, which collaboratively manages your design from a single source specification, turning address map sharing into a smooth, integrated process.

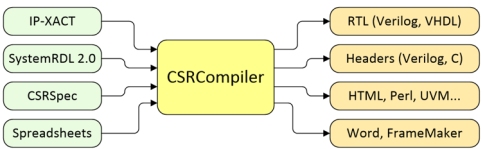

CSRCompiler offers a scalable and unified infrastructure to automate all aspects of HSI requirements throughout the design process (RTL, SW, DV, DOC). It can accept CSR definitions in multiple formats and provide alternate views of the data for use by different groups, such as RTL for hardware design engineers, header files for software developers and documentation for verification engineers (Figure 1).

Figure 1. CSRCompiler: Inputs and outputs. (Courtesy of Arteris)

In addition to being able to read anything from legacy spreadsheets to IP-XACT and its own CSRSpec format, CSRCompiler can both process and produce SystemRDL files. Today’s SoC developers will find it particularly interesting that CSRCompiler now supports the latest SystemRDL 2.0 standard.

As compared to its original incarnation, SystemRDL 2.0 offers an improved approach to defining registers and memories. It can now describe new elements such as memory components, alternate components, arrays and field structs. The tool also provides parameter support for configurable components to speed development and enhance design reuse for the automotive, communication, consumer, enterprise and industrial markets.

Conclusion

By centralizing and tailoring HSI information, CSRCompiler’s integrated HSI database serves the entire SoC development team, including architects, RTL designers, verification engineers, software developers and technical writers. As such, it eases collaboration across teams that all rely on a correctly implemented HSI to ensure a robust design.

CSRCompiler's flexible design allows it to integrate multiple input formats into a single source.

All inputs are verified for semantic and syntactic correctness, ensuring data is clean, verified and ready for use. Its comprehensive cross-compiler efficiently produces all required formats and prevents design mistakes during address map deployment, thereby ensuring first-time right outputs. Besides, it compiles thousands of registers in seconds and millions of registers in minutes, boosting productivity with a very fast performance.

With its ability to take full advantage of SystemRDL 2.0, CSRCompiler ensures consistency across multiple views and organizations without the need for time-consuming and error-prone manual scripting and editing. It gives the entire design team a complete, correct and up-to-date register design ecosystem. This approach can reduce the HSI development process by up to one-third, minimizing frustration, increasing productivity, reducing risk and speeding time to market.

About the Author

Insaf Meliane is a product management and marketing manager at Arteris. Before joining the product team, she was a field application manager, supporting customers with complex SoC design integration. Prior to joining Arteris, she held other design and application engineering roles at leading semiconductor companies. Insaf holds an engineering degree in microelectronics option system-on-chips from Ecole Nationale Supérieure d’Electronique et de Radioélectricité de Grenoble.