By Agnisys

The semiconductors business is incredibly competitive, with dynamic end markets and constant shifts in leading products and vendors. It takes excellence on many fronts to succeed, far more than I can cover in a single blog post. Thus, I’m going to focus on one particular aspect of developing competitive IP and system-on-chip (SoC) products: the ability to manage your register specifications and automate the process of turning them into silicon.

What Does It Mean to Be Competitive?

At the highest level, features (including quality) and price are the biggest factors when choosing one product over another. You can get a chain pizza for less than half the price of a gourmet pie from a local shop, but you don’t expect the same level of ingredients or taste. The semiconductor market is much more complicated, but the same elements are in play. A chip fabricated in an older process node is likely to be slower and have fewer features, but almost certainly less experience.

Electronic design automation (EDA) vendors often focus on power, performance, and area (PPA) as metrics for chip designs. Performance is a type of feature; area directly affects manufacturing cost and therefore the end price. Power consumption is also a feature, although it’s so important in some applications that it is called out separately. Many people would gladly pay a premium for a cell phone with longer battery life, even if it’s no better than the competition in any other way.

Given how quickly the semiconductor market changes, time to market (TTM) is also a big factor in success. Being the first with a new type of chip can be worth billions of dollars. Further, most chips are part of families that cover multiple markets, so the ability to spin variations quickly and to respond to competitive offerings is also critical. Faster, more automated silicon development flows both shrink TTM and reduce project cost, which helps keep the end price down.

The Role of Your Registers

Any modern IP or SoC design includes many addressable memory-mapped registers that allow the software to configure and control the hardware, and to receive back status. These are often referred to as control and status registers (CSRs), and they are a main component of the hardware-software interface (HSI). Low-level programs such as drivers, microcode, and embedded software can use the CSRs to operate the hardware and read back information on the results of those operations.

I’m sure that most of you know all that very well, but you may be wondering what registers have to do with having competitive products. For a start, they provide flexibility to configure the hardware for different applications. Specific features can be enabled and disabled, or different power/performance tradeoff points can be selected. This means that the same silicon can be used for multiple purposes without having to create new chips.

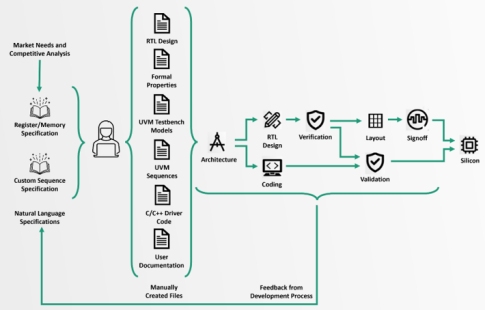

There are times when different applications require different CSRs, and often other hardware changes as well. In such cases, the ability to modify the registers easily plays a big role in being able to quickly spin out new design variations or to respond quickly when competitors introduce new products. This requires a much better development process than the one shown in Figure 1, in which all development files are created by hand from register specifications written in natural language.

Figure 1: Manual Register Development Flow

How to Be Uncompetitive

There are three major problems with the flow shown in Figure 1 that make it hard for IP and SoC teams to develop competitive products. The first issue is that the specifications for the CSRs, as well as any special sequences needed to access them, are written in a natural language such as English. Such a specification is inherently ambiguous, leading to different interpretations by different teams, or even different engineers within a single team.

The second issue is that all the key design, verification, software, validation, and documentation files are created by hand based on reading the specifications. Differing interpretations mean that these files do not always agree. Further, the very nature of the manual process means that human errors are inevitable, ranging from simply typos to fundamental misunderstandings. In any case, the result is a chip that does not operate properly, compromising PPA or missing key competitive functionality.

Finally, specifications change many times over the source of any IP or SoC project. New market opportunities or competitive pressure may lead to changes in the specifications. Issues uncovered during any stage of the development flow may feed back to the specifications, requiring changes. Every time that any specification changes for any reason, all the development files must be updated manually. This offers even more opportunities for errors or differing interpretations.

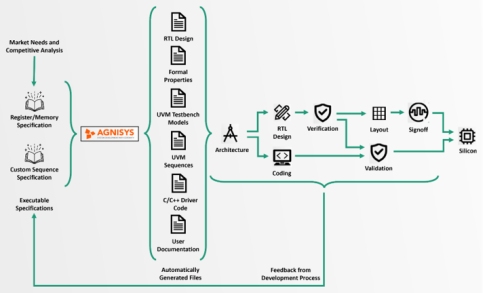

How to Be Competitive with Agnisys

The solution to all three issues is specification automation, specifically register specification automation. This flow starts with CSR and sequence specifications written in executable formats that are formally defined and unambiguous. EDA tools can read these executable specifications and automatically generate all the design, verification, software, validation, and documentation files that you had to create manually in the past.

Whenever a specification changes, your project team simply pushes a button to generate updated files. All files for all teams are correct by construction and always synchronized. There’s no need to debug design bugs due to the issues with the manual flow of Figure 1. The automated flow saves project time and resources, reducing TTM and making it easier to hit price targets. Design changes needed to accommodate new applications or competitive challenges happen quickly and correctly.

Figure 2 shows how this flow works using the Agnisys IDesignSpec™ Suite of specification automation tools. We accept a wide range of executable register specification formats, including the IP-XACT and SystemRDL standards. We also offer AI solutions that can generate executable specifications from some types of natural language specifications. We generate all the development files you need automatically not just once, but every time a specification changes.

Figure 2: Automation Register Development Flow

Summary

We know that you need to build competitive products and respond quickly to industry changes. A fully automated register development flow helps to make this possible. We have the experience and the expertise to help. Please contact us for more information, a demo, or an evaluation license.