By Innosilicon

1. Introduction

The market for audio applications and devices has significantly grown over the last couple of years. Applications such as smart speakers, Bluetooth speakers, smartphones, and voice-controlled human-machine interfaces (HMI) have gained great popularity, leading to a steady stream of new and improved audio devices. All these applications integrate an audio codec, which is responsible for converting an analog audio signal to a digital audio signal and vice versa. The audio codec performance directly impacts the sound quality of the device, which makes it one of the most important functions of an audio system.

This white paper will explore the technology and features of high-performance audio codecs. It will explain commonly used technologies such as sampling rate, quantization, signal-to-noise ratio (SNR), oversampling, and Sigma-Delta modulation. The use of compression algorithms, such as MP3, AC’97 is beyond the scope of this paper. This paper will only discuss the details and importance of analog-to-digital converter (ADC) and digital-to-analog converter (DAC) of a codec.

Finally, this paper will highlight some of the typical challenges IC designers face when integrating an audio codec into their system or SoC. It will be shown how implementing an off-the-shelf audio codec is an option to increase time-to-market and limit the design risk while also maintaining customizability and flexibility.

2. CODEC Overview

A codec (coder-decoder or compressor-decompressor) is a function used to encode and decode data, such as audio, video, or other types of files. It transforms raw data into a compressed format to save storage space or reduce transmission bandwidth and then converts it back into its original form. Often, a codec is combined with a digital-to-analog (DAC) and an analog-to-digital (ADC)converter, which converts an analog signal into a digital signal and vice versa. Depending on the application requirement, many compression algorithms exist, e.g. MP3, MP4, AC’97, WAV, and can be integrated into the codec.

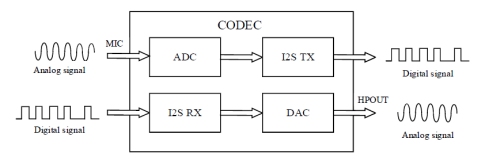

The two important functional blocks of audio codec architecture are the Analog-to-Digital Converter (ADC). and the Digital-to-Analog Converter (DAC), as they directly impact the audio quality. The digital audio signal can be connected to other integrated circuits (IC) components via an Inter-Integrated Circuit Sound (I²S) interface. This is a serial interface protocol for transmitting two-channel, digital audio a pulse-code (PCM) signal. (Figure 1 Audio Codec Block Diagram) shows the functional structure of a codec discussed in this paper.

Figure 1 Audio Codec Block Diagram

3. Codec Features

Sampling rate

The sampling rate of an audio codec refers to the number of times per second an audio signal is sampled to create a digital representation of the analog signal. It is measured in Hertz (Hz) and determines the audio quality and the range of frequencies that can be captured.

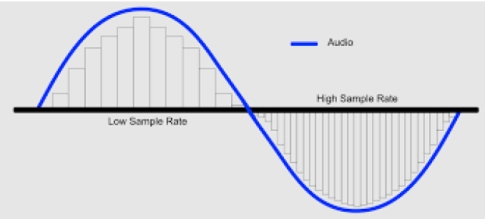

The physical theory is based on the Nyquist Theorem, also known as the Nyquist-Shannon Sampling Theorem, which describes the fundamental principle of digital signal processing. The theorem asserts that to capture all the information in a signal without losing any data, the sample rate needs to be at least twice that of the signal's highest frequency (Figure 2 Sampling Rates).

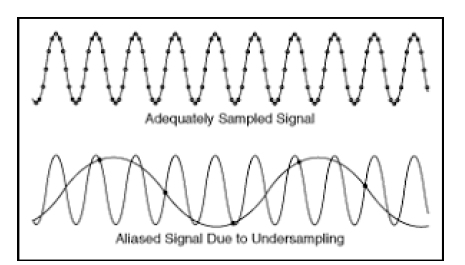

If the sampling rate is below the Nyquist rate, distortion occurs, and higher frequencies are indistinguishably reflected as lower frequencies. This distortion is called aliasing (Figure 3 Aliasing Distortion).

Source: https://www.hollyland.com/blog/tips/what-is-sample-rate-in-audio

Figure 2 Sampling Rates

Source: https://www.ni.com/docs/en-US/bundle/labwindows-cvi/page/advancedanalysisconcepts/aliasing.html

Figure 3 Aliasing Distortion

Some of the most common audio sampling rates are:

- 44.1 kHz: The standard for CDs, capturing frequencies up to 22.05 kHz.

- 48 kHz: Common in professional video and audio equipment, capturing frequencies up to 24 kHz.

- 88.2 kHz and 96 kHz: High-resolution audio format, for higher fidelity.

- 192 kHz: High-end audio equipment, ultra-high fidelity.

Integrated circuit (IC) designers must make a trade-off when designing their audio system. They must decide between high-quality audio with a high sampling rate or low power and minimum silicon area. Power, performance, and silicon area optimization, known as PPA optimization, is becoming an important factor in deciding whether to develop or buy functional building blocks for ICs.

Quantization

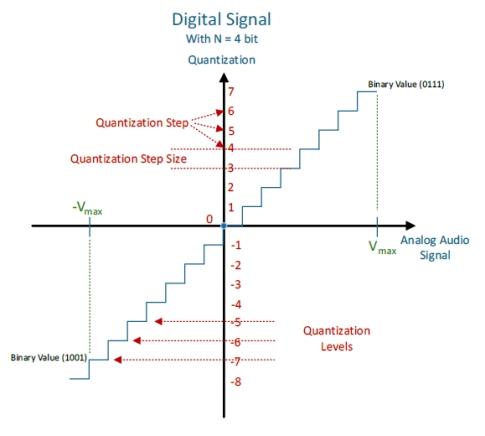

Quantization in an audio codec is the process of mapping a continuous analog audio signal to a discrete digital signal by taking continuous amplitude samples and approximating them to the nearest value in a finite set of levels. A quantizer uses predefined steps, splitting the analog signal into equal intervals. These intervals are called step sizes (Δ). When converting an analog audio signal to a digital signal, quantization involves mapping the amplitude of the signal, measured in Volt, at each sampling point to a discrete digital value. This method is depicted in Figure 4 Analog Voltage Quantization). In this example, a 4-bit quantizer (N=4) is used to encode the different voltage levels to a finite digital level. The quantizer uses four bits to represent one of the 16 different voltage levels, which is called the quantization step.

The voltage value -V max has the Quantization Step of (-7) and is represented by the four bits " 1001 ", which means that the analog voltage -V max is encoded as " 1001 ". The voltage level Vmax corresponds to the Quantization Step of (+7) and is encoded into “0111” (Figure 4 Analog Voltage Quantization). If a voltage level does not fall on a specific Quantization Step the quantizer uses an algorithm, such as rounding or truncation to map the actual value to the closest approximate nearby quantization step.

Figure 4 Analog Voltage Quantization

Quantization is a critical step in the digitization of analog audio signals. If the chosen quantization step size and quantization steps are inappropriate, an algorithm for approximation will be used and consequently a quantization error will be injected into the digital signal, which will result in signal noise, making it difficult to reconstruct the original audio signal. This will lead to a loss of audio quality.

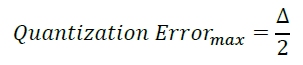

Quantization Error

An audio quantization error is the difference between the original audio analog value and the nearest quantized digital value. The error occurs because the analog signal is approximated to the nearest discrete level, resulting in a small loss of accuracy and audio quality. The expected quantization error is directly proportional to the step size. As the step size increases, the quantization error increases. Conversely, reducing the step size decreases the quantization error. The maximum quantization error can be described as half the step size.

IC design engineers need to understand and define the maximum accepted quantization error, the impact of the chosen step size, and the implication for their system design, as it directly impacts the audio quality. For example, if the step size is large, each audio value is approximated, leading to a higher quantization error. On the other hand, if the step size is small, the audio value is approximated more closely, resulting in a lower quantization error and better audio quality. The drawback is that a smaller step size requires more quantization bits for the ADC, increasing design complexity

Signal-to-Noise Ratio

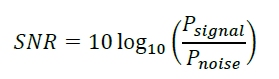

The signal-to-noise ratio (SNR) measures the level of a desired original audio signal compared to the level of background noise.

It is expressed in decibels (dB) using the formula

SNR is used to measure and evaluate the quality of the codec. A higher SNR indicates clearer, better audio quality with less noise, while a lower SNR indicates a noisier audio signal where the noise is more prominent.

Relationship of SNR and quantization step

SNR and quantization are closely related. Specifically, the quantization step size directly affects the level of quantization noise and consequently, the SNR. The SNR in the context of quantization can be expressed as a function of the number of quantization levels or bits (N=bits) and the step size. For a uniform quantizer with a mid-tread quantization, the SNR in dB is approximately:

![]()

This means that with a 1-bit increase in quantizer resolution, the signal-to-noise ratio will increase by 6.02dB.

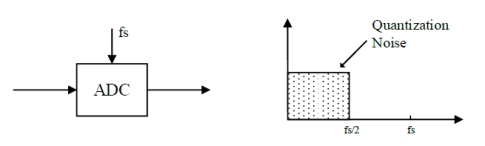

Oversampling,

Oversampling is a technique to improve the resolution and quality of digital audio signals. It involves sampling the signal with a significantly higher rate (K*fs) than the minimum required rate, defined by the Nyquist theorem (fs). Oversampling is commonly used in audio processing applications.

Oversampling of an audio signal provides several key benefits. First, it improves the audio signal resolution, leading to an accurate representation of the audio signal. Second, it reduces the signal quantization noise as the total noise level is spread over a broader frequency range. An adequate filter can filter out the noise more easily and improve SNR. Third, digital filters can be used for down-sampling or decimation. This will reduce the sampling rate to the desired level while preserving the improved audio signal resolution and noise reduction benefits. Fourth, oversampling can enhance the dynamic range of a signal, which is the difference between the smallest and largest possible values of a signal

Figure 5 Nyquist Frequency Sampling & Quantization Noise​

Figure 6 Oversampling & Quantization Noise

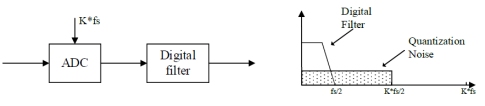

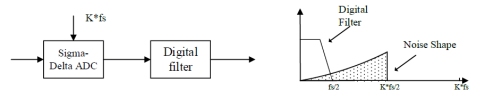

Sigma-Delta Modulation

As the use of oversampling will improve the SNR of an ADC, it has some drawbacks. For example, an increase in the sampling frequency will lead to an increase in the power consumption of the IC. Sigma-Delta-Modulation is a method that will further improve the SNR by using a noise-shaping technology Figure 7 Noise Shaping & Quantization Noise). This technology shapes the uniformly distributed quantization noise as depicted in Figure 6 Oversampling & Quantization Noise), pushing most of the quantization noise to higher frequencies. This high-frequency noise can be filtered out with a digital filter, improving the SNR (Figure 7 Noise Shaping & Quantization Noise).

Figure 7 Noise Shaping & Quantization Noise

4. Audio Codec Applications and Design Challenges

Audio codecs are widely used in various applications such as smart speakers, voice assistants using artificial intelligence, streaming & playback of audio and voice, home audio, voice-over internet (VoIP), digital broadcasting, gaming, automotive, hearing aid, earbuds, HMI, Industrial IoT, predictive maintenance, and others. All these applications have unique requirements in terms of expected audio quality, size, or the way they are powered.

Designing an audio system presents several challenges for chip designers. These challenges can be divided into IP design and integration challenges. Some of the most important key considerations are:

IP Design Challenges

High-Quality Audio Performance: Achieving a high Signal-to-Noise Ratio (SNR) and minimizing signal errors require precise analog design. Maintaining consistent performance across temperature, voltage, and process variations adds to the complexity.

Power Consumption: For battery-powered devices such as smartphones, portable Bluetooth speakers, and wireless earbuds, an energy-efficient audio codec is essential for maximizing operation on a single charge. Designers need to decide on the appropriate sampling rate and architectural implementation.

Cost and Area: Silicon area is directly proportional to cost. Designing the codec to occupy minimal silicon area while maintaining performance is crucial for cost-effective production.

Testing and Validation

Designers must specify the best method for Design for Testability (DFT) in the IC. Rigorous testing is required to ensure the codec meets all performance and quality standards, is time and resource-consuming.

Make vs. Buy

Buying an off-the-shelf audio codec requires identifying IP that is flexible enough to meet all design requirements, scalable, and silicon-proven from an IP partner with deep expertise and expert knowledge. This IP partner needs to have experience with multiple foundries and process technologies.

Integration Challenges

Power Consumption: For battery-powered devices, an energy-efficient audio codec is essential for maximizing operation on a single charge. Power leakage, which largely depends on the silicon manufacturing process technology, plays a crucial role, as these devices spend most of their time in standby mode.

Process Technology: Unlike digital circuits, analog circuits do not scale as efficiently with newer process technologies, which can affect both performance and cost. Designers must carefully select the optimal process technology to meet their application requirements.

Thermal Management: Managing heat dissipation is crucial to prevent overheating and ensure device reliability. Additionally, extra cooling increases product cost and requires more space for heatsinks or fans.

SoC Integration: Ensuring signal immunity from interference is crucial when integrating the codec into a System on Chip (SoC). This requires careful planning to minimize signal crosstalk and maintain optimal performance. System designers must ensure the codec is resistant to electromagnetic interference (EMI) and radio frequency interference (RFI).

5. Summary

An audio codec is a complex system and developing a scalable high-reliable, high-performance, and low-power audio codec is not an easy task. The mathematics and technology behind an audio codec is quite complex. Integration into a SoC and testing opens a new set of challenges for IC designers. Addressing the design challenges requires advanced engineering techniques, innovative design strategies, expert knowledge, and monetary and human resources. These resources are often limited.

Using an off-the-shelf, silicon-proven audio codec IP that seamlessly integrates into the SoC is an effective solution to overcome these design challenges. It accelerates time-to-market, reduces design risk, optimizes resource utilization, and ensures high product quality from the first silicon.

Innosilicon Technology Inc. has developed a highly flexible and customizable advanced audio codec featuring a Sigma-Delta architecture. It supports sampling rates of up to 96 kHz with an impressive SNR of up to 93 dB and up to 24-bit quantization. Designed for an immersive audio experience, the codec offers up to 8 channels, accommodating mono, stereo, 5.1, and 7.1 HiFi performance. This high-performance, off-the-shelf solution has been extensively tested, integrated, and silicon-proven across multiple foundries and process technologies ranging from 55nm to 6nm, making it ideal for a wide range of audio applications.

6. About Innosilicon

Innosilicon, is a global leading provider of High-Speed IP and ASIC design services. Founded in 2006 the company has established itself as a reliable IP provider and built a well-recognized reputation in the semiconductor industry. Innosilicon supported over 300 top-tier clients, enabling them to increase their time-to-market and limit design risk, shipping more than 10 billion high-end SoCs. Innosilicon is committed to accelerate global innovation by leveraging its extensive chip design expertise and deep partnerships with semiconductor foundries, like TSMC, Samsung, Global Foundries, and others, striving toward customer success. During the last two decades, the company has worked on applications, such as high-performance computing, multimedia, automotive, AI, and IoT applications and developed an intensive IP portfolio ranging from HBM3E, GDDR7/6X/6, UCIe Chiplet, and PCIe5 and others.

Innosilicon Technology Inc.

97 E Brokaw Rd #210,

San Jose, CA 95112

For more information, contact sales@innosilicon.com

www.innosilicon.com