Industry Articles

Discover new Tessent UltraSight-V from Siemens EDA, and accelerate your RISC-V development.-March 24, 2025 |

By Dr. Francisca Tan, Tessent Embedded Analytics

As the RISC-V ecosystem continues to grow, the need for robust verification and debug solutions remains increasingly important. However, the time, effort and cost of debugging and optimizing software running on current multi-core SoCs also continues to escalate as design complexity increases.

Consequently, more efficient methods to debug, iterate, and scale such systems are required to identify hardware and real-time software issues in these systems.

Tessent UltraSight-V, brought to you by the Tessent Embedded Analytics team at Siemens EDA, is designed to address these challenges and to help streamline the RISC-V design process.

A new, comprehensive, end-to-end debug & trace solution for RISC-V based SoCs, Tessent UltraSight-V is specifically designed to support and enable embedded software engineers to develop high-performance embedded software, whilst maintaining compliance with the official RISC-V trace specification.

The solution is built on a combination of embedded IP and software, and utilizes effective, non-intrusive techniques and processor trace based on the Efficient Trace (E-trace) standard, to minimize debugging delays and accelerate SoC projects, to help meet market deadlines.

Key features & benefits include:

- End-to-end debug and trace solution for RISC-V SoCs

- Highly compressed processor trace (RISC-V E-Trace spec)

- Fast system memory access for ELF file uploads

- Code instrumentation for logging to provide added visibility and performance analysis

- Uses high speed transport interfaces (USB 2.0) that are suitable for bare metal access thus simplifying debug access port design

- Scalable to a complete SoC system-level debug, optimization, and monitoring solution

A highly compressed trace solution for RISC-V processors

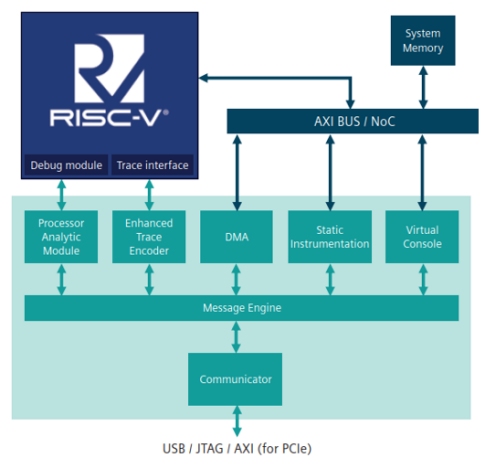

Complex systems are prone to imperfect software behaviors. Tessent UltraSight-V’s Enhanced Trace Encoder (ETE) provides a mechanism to monitor a CPU’s program execution in real time. It encodes instruction execution and, optionally, data memory accesses. It also outputs trace in a highly compressed format, significantly saving bandwidth especially in large complex systems. The device execution can be fully reconstructed offline. The non-invasive ETE works with minimal latency, so it does not affect performance.

Filtering the trace can help you investigate a problem further. The Enhanced Trace Encoder supports all the mandatory and optional capabilities in the E-Trace specification. It can also provide cycle-accurate trace, which can provide insight for software performance optimization.

A complete debug and trace solution for RISC-V processors

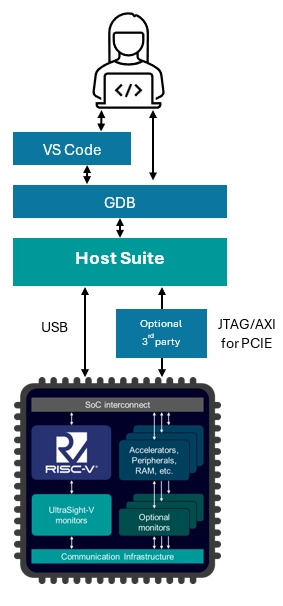

Tessent UltraSight-V includes a set of IP modules and host software that provide extensive visibility into how the software application behaves in the system. The Processor Analytic Module provides run control capabilities. The Direct Memory Access IP module allows code to be uploaded to the SoC 70-100X faster than normal GDB load. The Static Instrumentation IP module allows printf-style debugging with timestamps to be accomplished with 20X fewer instructions. The Virtual Console module provides a bidirectional communication channel between software running on the target and the debug host. It replaces conventional UART-based communication with no need for an additional physical port. A scalable dedicated infrastructure ensures non-intrusive monitoring. This infrastructure is accessed through USB, JTAG or PCIe interfaces. The host software in UltraSight-V integrates with GDB, OpenOCD and common IDEs such as VS Code.

Discover Tessent UltraSight-V | Live Webinars – 1 April 2025

Learn how to streamline your RISC-V development process and deliver high-quality designs faster with Tessent UltraSight-V, by attending one of our free live webinars.

Our Product experts will showcase the tool's key features and demonstrate how it can benefit your RISC-V development efforts.

Some of the topics we'll cover in the webinars include:

- Comprehensive RISC-V verification with advanced debug and analysis capabilities

- Seamless integration with popular RISC-V development environments, such as Eclipse and Visual Studio Code

- Efficient debug and triage of complex RISC-V designs using the Tessent Debugger's powerful analysis and visualization tools

- Optimized performance for faster time-to-market through the use of coverage-driven verification and formal analysis techniques

Learn more & register:

Europe Webinar | 10am BST | 1 April 2025

Free registration here

USA Webinar | 9am PDT | 1 April 2025

Free registration here