Bytom, 25th of April, 2013 -- The DP8051 is the 5th consecutive uncover of the 8051 IP Cores in Digital Core Design’s portfolio. Like its kinsfolk, it’s described by simplicity, high efficiency and performance. But unlike the competitive designs, it runs Dhrystone 2.1 benchmark program 11.46 to 15.55 times faster, which means, that this Pipelined RISC architecture executes up to 300 million instructions per second.

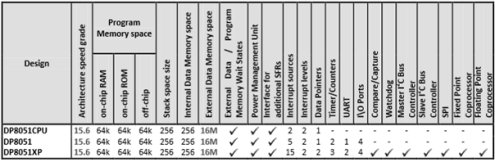

The DP8051 is a high performance, speed optimized soft core of a single-chip 8-bit embedded controller, intended to operate with fast (typically on-chip) and slow (off-chip) memories. Broad set of additional features and peripherals let the engineer to tailor the core to the specific application and/or hardware requirements. Moreover, the core has been designed with a special concern about power to performance ratio - This ratio is extended by an advanced power management PMU unit – explains Tomasz Krzyzak, VP, Member Board of Directors at Digital Core Design – also there’s a bunch of serviceable peripherals available e.g. 2-15 interrupt sources, 4 interrupt levels, 2 data pointers, USB device, Ethernet controller, up to 4 timer/counters, 2 UARTs, 4 I/O ports and more. Depending on the configuration, the designer can likewise choose from e.g. compare/capture, watchdog, master/slave I2C Bus controller, Quad SPI, fixed point copro-cessor or a floating point coprocessor.

The Dhrystone 2.1 benchmark score for the DP8051 shows speed improvement from 11.46 to 15.55 over Intel® 80C51 at the same frequency. The same C compiler was used for benchmarking the core vs. 80C51, with the same settings. This performance can be also utilized as a great advantage in low power applications, where the core can be clocked over ten times slower than the original implementation, without performance depletion.

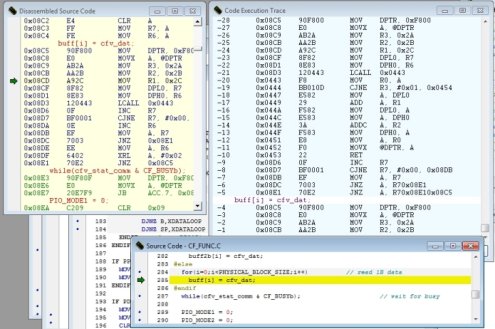

The DP8051, like all other DCD's 8051 IP Cores, has a built-in support for the DoCDTM Hardware De-bugger, which provides debugging capability of a whole System on Chip (SoC). Unlike other on-chip debuggers, the DoCDTM provides non-intrusive debugging of a running application. It can also effi-ciently save designer’s time, thanks to hardware trace, called Instructions Smart Trace buffer (IST). The DoCD-IST captures instructions in a smart and non-intrusive way, so it doesn’t capture addresses of all executed instructions, but only these related to the start of tracing, conditional jumps and inter-rupts. This method does not only save time, but also allows to improve the size of the IST buffer and extend the trace history. Captured instructions are read back by the DoCD-debug software, analyzed and then presented to the user as an ASM code and related C lines.

More information about DP8051: www.dcd.pl/ipcore/34/dp8051/

|youtubevideo:zSk-NfyK-5I|

More details about DCD on Chip Debugger: http://www.dcd.pl/page/154/docd/

DoCD’s Instructions Smart Trace Buffer

The DP8051 family overview

CPU FEATURES: