Dresden (Germany) and Bengaluru (India), Jun. 06, 2016 – Fraunhofer IIS/EAS, a leading research institute focusing on design solutions for chip packages and integrated systems, and SilabTech, a leading supplier of high speed interface intellectual property designs (IP cores), announced today their holistic solution for chip-to-chip interconnection. The solution combines the break-through interposer packaging technology from Fraunhofer with SilabTech's JESD204B high speed serial interface IP core.

The new generation of high speed and high resolution ADCs/DACs drive a new wave of products in the areas of communication, RF as well as test and measurement. Large amount of data - up to 10's of Gbps - must be transferred between the ADCs/DACs and the host processor chip inside these systems.

An interposer based integration of ADCs/DACs and host processor is particularly well suited to meet the increased performance requirements of high speed chip-to-chip communication. Here, the circuit integration based on separate chip packages and FR4 PCB reaches its limits since further reduction of the link power budget as well as the footprint of the solution is not possible. In addition, latency, skew and alignment issues for high data rate SERDES links are difficult to solve because the production accuracy and repetitiveness of PCB technologies is limited.

Heterogeneous Interposer-Based System Interconnection

Solution Approach

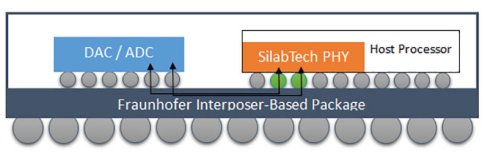

In this demonstrator the host processor and ADCs/DACs are placed as bare dies on a single interposer which is then packed into a single package. The very short physical interconnections on the interposer were designed to transmit signals with a bandwidth up to 50 GHz; the associated production process ensures very high repetitive accuracy during mass production. In this design SilabTech's 6.25 Gbps JESD204B SERDES and controller were integrated to the host processor chip and manufactured on 28nm low power process. The 8 lane configuration provides 50 Gbps pipe between the chips with potential to go up to 200 Gbps with the new 28 Gbps SERDES.

Due to the high IO density and the small line/space which is available for silicon interposer based packaging technology, this 8 lane chip to chip interconnection will only need 320 µm of width on the interposer. This is significantly less space than any other solution offered in the market.

Shorter conductor paths also consume significantly less energy, which positively impacts the energy profile, long term reliability and the lifetime of the device.

The adaptation of new silicon based interposer technology along with high speed Serial Interfaces is enabling designers to meet the demand for increased data rates while keeping power and the required space at the minimum.

For more details on Fraunhofer IIS/EAS and SilabTech please visit www.eas.iis.fraunhofer.de and www.silabtech.com

About SilabTech

SilabTech is a silicon fabless company that was established in 2012 to bring innovative design approaches to the ever increasing challenge of chip-to-chip and backplane high speed connectivity. The company has a track record of building high speed SERDES IP cores and in integrating them at chip top level. SilabTech specializes in low power processes and advance nodes such as 28 & 40 nm. Among the company customers are top multinational fabless IC companies, system companies and ASIC design houses.

About Fraunhofer Institute for Integrated Circuits IIS, Engineering of Adaptive Systems EAS

The Fraunhofer Institute for Integrated Circuits IIS is one of Germany's most important research facilities for the development of microelectronic systems. The scientists in the Division Engineering of Adaptive Systems EAS in Dresden develop methods and tools to reliably design increasingly complex electronic and mechatronic systems. This optimizes and accelerates implementation of product requirements in circuitry, devices or complex sensor systems. The division also focuses on innovative in-house developments. The results of the work are used in a broad range of application areas e.g., in communication, automotive and automation technology.